FPGA的核心控制系统是由1 400~1 800 LE构成的,运行起来可以到达86DMIPSD的f型NiosⅡCPU。除了CPU外,数控系统主要还包括一个标志NiosⅡ系统的系统ID核;一个提供JTAG串行异步收发器的IP核,用于在线调试FPGA的程序;一个可以实现任何标准RS 232标准波特率的UART核,用在控制电路调试成功后在单机工作状态下与外接计算机通信;两组并行输入、输出PIO核,分别对A/D采样电路进行控制和读取A/D采样后得到的数据;两个LCD控制器IP核;一个用于运行程序的片内ROM;一个提供系统时钟的PLL;一个EPCS串行配置器件控制器IP核。如图5所示。

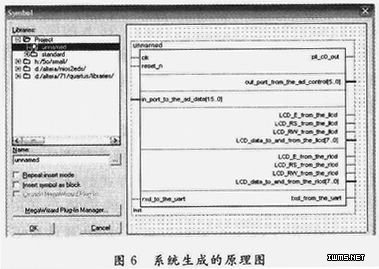

系统生成的原理图如图6所示。

3 系统开发测试

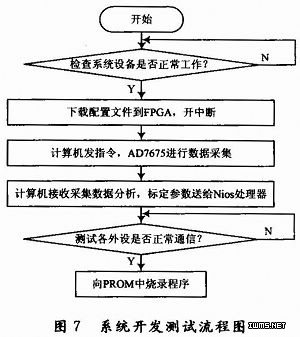

系统构建好之后,需要进一步的测试才能确保其正常测温。系统的开发测试流程如图7所示。

上电后首先观测系统的主要硬件是否正常工作,将在NiosⅡIDE中生成的SOF文件下载到FPGA中,完成NiosⅡ系统的下载和初始化。然后将NiosⅡ软件通过JTAG口下载到目标系统中。系统正常工作后,由远端计算机通过串口对A/D进行初始化,采集数据。计算机接收到A/D采样数据后,就可以对测温器进行标定,通过数据处理计算出用于标定各台测温器的校准方程。

标定过程如下,将测温器红外接收探测头对准热源,热源产生准确的温度。为了测量准确,对于同一个温度点,采用多次测量取平均值的方法。由计算机通过串口通信记录下多次A/D采样的值与对应的温度值。从低温开始到较高的温度,由计算机通过串口通信记录下A/D采样值。当记录下的数值达到可以反映各温度段变化的情况时,就可以让计算机采用合适的数据拟合方法生成反映该测温器测量特性的曲线方程。计算机将方程系数传送给NiosⅡ系统,完成对整个测温器的校准。

最后检查FPGA中NiosⅡ处理器能否通过LCD控制器与LCD正常通信、LCD能否正常显示字符;NiosⅡ软处理器可否与PROM实现正常的读写。调试成功后为了节约资源可将JTAG调试去掉,然后将正确的程序烧录到EPCS4中。这时所设计的程序即可脱离计算机及NiosⅡIDE独立运行。

完成了整个开发过程的测温器即可正常使用,对标定温度范围内的温度进行测量。脱机测量时,由定时器产生对A/D采样时所需的时钟脉冲,NiosⅡ系统的两组PIO,分别控制A/D的控制信号和将A/D采样值读入NiosⅡ系统。在使用时,仍然采用多次测量取平均值的方法来得到A/D采样值,然后根据拟合方程,即可得到对应的温度值,然后NiosⅡ系统控制LCD控制器的R/W,RS和DB0~DB7,将对应的温度值显示在

LCD上。而当需要联机使用时,NiosⅡ系统通过串口将存储在内部的A/D采样值和对应的温度值发送到计算机中,形成文件供分析用。

4 结语

本文设计的测温器的数控电路以ALTEra公司的CycloneⅡ系列的FPGA为核心,完成了从总体方案设计到系统调试等一系列过程。整个数控系统共计占用3 700多个LE,99 200个存储器比特。为整个测温器提供了稳定可靠的数据处理平台,可为更高级别的功能扩展提供一定的参考,具有很广的应用前景。