・上一文章:带编、译码的无线电遥控器(10m)

・下一文章:CDMA 2000系统中前向链路卷积编码器的FPGA实现

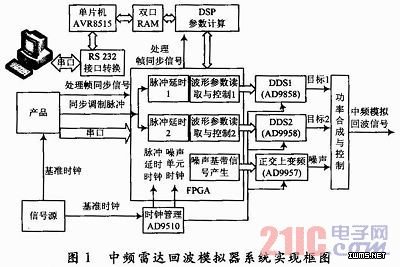

该模拟器通过单片机(AVR8515)与上位机进行异步串行通信,单片机完成通信协议的解包、打包等过程,接收上位机中用户设定的目标和干扰参数,发送模拟器的实时模拟状态信息给上位机。系统以DSP(ADSP-21060)作为脉冲参数的实时计算单元,单片机与DSP问通过双口RAM进行信息交换。DSP得到两个目标的模拟参数后,根据参数变化的时间节拍,计算一个相参帧两目标的各脉冲的初相、载频、脉冲延时等参数,并写给双口RAM。系统以FPGA(XC2V3000)作为信号处理与控制单元,FPGA读取后,在产品提供的处理帧同步信号和同步调制脉冲控制下,结合产品串口传过来的波形类型的信息(如:脉内单频还是线性调频),形成两个目标的延时脉冲,并控制两个目标各自的DDS(AD9858)信号产生单元,产生出两个目标信号。带限的高斯白噪声的数字正交基带也由FPGA产生,并同步AD9957的数字正交上变频功能将基带调制到所需的中心频上。目标1、目标2和噪声信号的合成由模拟电路实现,并实现一定的功率控制,最后输出所需的中频雷达回波信号。模拟器系统各单元时钟的相参性至关重要,由专用时钟管理芯片(AD9510)产生FPGA,AD9858,AD9957的工作时钟。

3 关键模块设计

3.1 数字延时模块

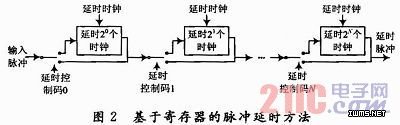

对于脉冲的数字延迟的实现,方法1是将DSP计算得到的延时时钟个数值D,转换为N位的二进制码,利用二进制码进行控制。可采用如图2基于寄存器的方法实现,这种方法优点是没有固定延迟,最小可实现零延迟。但当N增大时,此法耗费的FPGA触发器资源呈几何级数增加,因此,不适用于需要实现很大延时的场合。