・上一文章:带编、译码的无线电遥控器(10m)

・下一文章:CDMA 2000系统中前向链路卷积编码器的FPGA实现

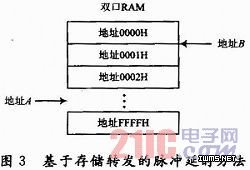

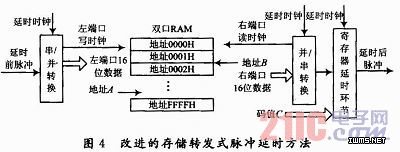

方法2避免了大延时情况下触发器资源过度耗费,但存在固定延时,另当延时时钟频率很高时,双口RAM的读写速度难以满足要求。因此,本系统在实践中对方法2进行了改进设计,如图4所示。

本设计将待延时的脉冲经延时时钟采样后,经串并转换形成16 b的数据,每16个延时时钟完成一次串/并转换,并输出一个16 b宽度的双口RAM的左端口写时钟,地址A仍按序累加。将地址A末位补上四个“1”构成宽地址x;x—D=Y(补码形式);式中:D为DSP计算的延时时钟个数值。将Y(二进制)的低四位提取出来作为码值C;其余高位构成图中双端口RAM的右端口读地址。其读时钟由图右的并/串转换单元每16个延时时钟周期输出一个脉冲;并/串转换单元将读出的16位数据转换恢复为脉冲,经过如图1寄存器方式实现的4位寄存器延时环节(控制码为码值C)延时后,输出延时后的脉冲。

该方法将双口的读写时钟降速到延时时钟的16分频,大大降低了双口RAM的速度压力,更易于实现。另16 b的双口RAM也可借助片外双口RAM实现,降低对FPGA存储资源的依赖。该方法的缺点是有更大的固定延迟,虽在延时大时可预先由DSP修正控制值,但对要求延时小于其固定延时的情况则无法适用。本系统综合采用两种方法解决,即:DSP输出码值的最高位决定延时方法的切换,当需求的延时大于固定延时时则采用图4的方法;而需求的延时小于固定延时时采用图2的寄存器法。