本文论述一种自主产生式的雷达回波模拟器中频部分的设计实现方法,该模拟器可产生脉冲单频、脉冲线性调频、步进频、步进频+线性调频等多种波形的雷达回波信号,并可产生双目标和参数可控的带限高斯白噪声,可模拟主要的干扰类型;输出信号既可以直接用于信号处理机的中频注入式测试,也可上变频后用于雷达系统的射频条件下的各种测试验证。以下对该中频雷达回波模拟器的实现方法予以详细阐述。

1 回波信号理论分析

按照设计要求,该模拟器需要模拟脉冲单频、脉冲线性调频、步进频、步进频+线性调频共四种波形的信号。其中,步进频又包括顺序步进频和随机步进频两种类型。这些波形的雷达回波信号,均可以统一表示为式(1)的形式:

式中:c为光速;N为相参帧的脉冲总个数;i表示相参帧内的第几个脉冲;To为脉冲宽度;Tr为脉冲周期;fc为相参帧内首脉冲的载频;△f为脉冲间最小步进频差;bi△f为第i个脉冲在初始载频基础上的频率变化(仅适用于脉间频率捷变波形,非脉间捷变波形则bi=0);k为线性调频波形时的脉内调频变化率(非脉内线性调频则k=0);Ro为目标当前距离;v为目标当前速度。

由以上分析可知,无论上述何种波形,均可根据式(1)计算脉冲的延时、每个脉冲的脉内初相、以及每个脉冲的载频等参数,并对这些参数在与产品同步的基础上予以实时控制来进行模拟实现。根据发射波形,还要决定是否添加脉内频率线性调制。

2 回波模拟器系统设计

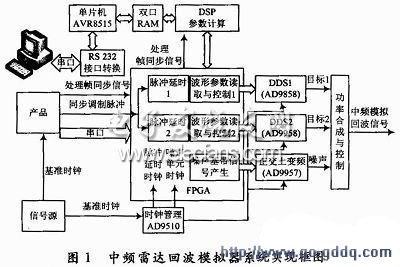

根据系统需求和前述雷达回波信号理论分析,该中频雷达回波模拟器(以下简称模拟器)采用了如图1所示的系统实现方案。

该模拟器通过单片机(AVR8515)与上位机进行异步串行通信,单片机完成通信协议的解包、打包等过程,接收上位机中用户设定的目标和干扰参数,发送模拟器的实时模拟状态信息给上位机。系统以DSP(ADSP-21060)作为脉冲参数的实时计算单元,单片机与DSP问通过双口RAM进行信息交换。DSP得到两个目标的模拟参数后,根据参数变化的时间节拍,计算一个相参帧两目标的各脉冲的初相、载频、脉冲延时等参数,并写给双口RAM。系统以FPGA(XC2V3000)作为信号处理与控制单元,FPGA读取后,在产品提供的处理帧同步信号和同步调制脉冲控制下,结合产品串口传过来的波形类型的信息(如:脉内单频还是线性调频),形成两个目标的延时脉冲,并控制两个目标各自的DDS(AD9858)信号产生单元,产生出两个目标信号。带限的高斯白噪声的数字正交基带也由FPGA产生,并同步AD9957的数字正交上变频功能将基带调制到所需的中心频上。目标1、目标2和噪声信号的合成由模拟电路实现,并实现一定的功率控制,最后输出所需的中频雷达回波信号。模拟器系统各单元时钟的相参性至关重要,由专用时钟管理芯片(AD9510)产生FPGA,AD9858,AD9957的工作时钟。