TCLGU21机芯高清彩电属于数字窗系列,是在NU21机芯基础上派生出来的,主板电路完全一样,仅数字板.f二的倍行处理部分不一样,NU21机芯倍行芯片采用PW1235A,该机芯采用FLI2300,不仅电路结构简单,而且新增了许多功能。GU21机芯的代表机型是H1D34158H。

FLI2300是微科公司生产的最新总线控制型数字解码及的数字变频主芯片,其PAL制图像具有以下几种成像模式:100Hz逐点清晰、60Hz数字逐点、75Hz数字逐点、152()线数字增密;NTSC制图像具有60Hz数字逐点成像功能。

一、数字板简介

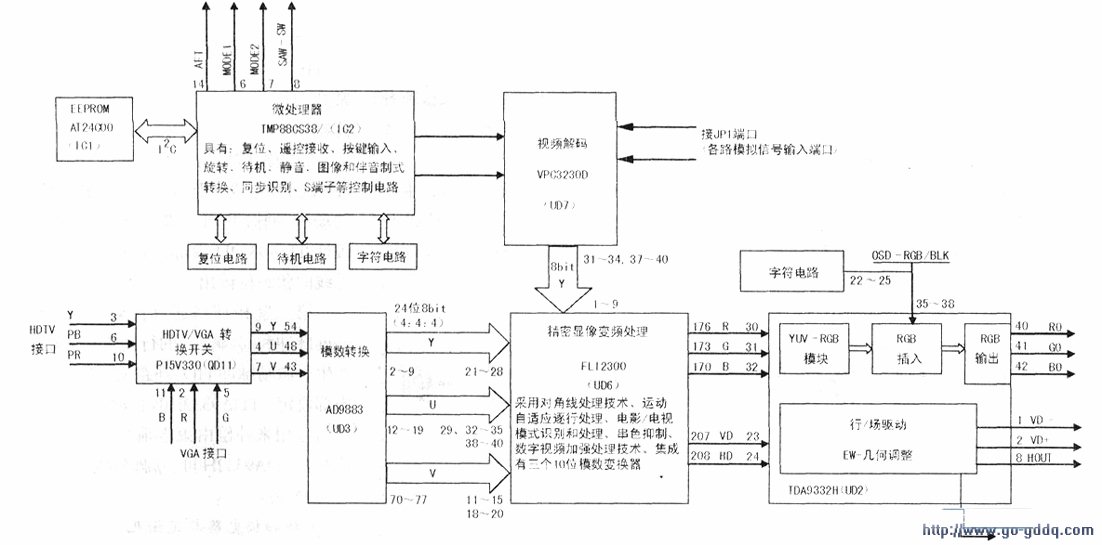

GU21机芯数字板电路主要由CPUTMP88CS38N(IC2)、24C00(IC1)、P15V330(QD11)、AD9883(UD3)、VPC3230D(UD7)、FLI2300(UD6):KM432S2030(UDl)、TDA9332H(UD2)等集成电路及一些外围元件组成,其组成框图见下图。

GU21机芯数字板通过JP1~JP5五个插座与外部电路连接。其中,JP1为从主板送过来的隔行模拟视频信号及ABL、FBP、VD+、VD-、VFB、EW、EHT、12V、5.2V电源等信号,输入的模拟信号进入VPC3230进行视频解码;IP2为遥控信号、按键信号、总线数据,与主板S001A的端口相连接;JP3为RGB,及消隐信号输出到CRT板;IP4为HDTV的信号输入端口;JP5为VGA的RGB及HS、VS同步信号输入端口。

所有的隔行视频信号都输入到视频解码器VPC3230D内部。VPC3230D是微科公司生产的梳状滤波视频处理器,该芯片集成了视频切换、Y/C分离(4H自适应梳状滤波器)、A/D转换、数字解码、pIp等功能。视频解码输出支持ITU-R601/656数字输出接口。

二、数字板信号流程分析

1.TV及隔行视频输入信号

一体化高频头输出的TV视频信号经电容CD131、RD130平滑滤波后,从VPC3230D(75)脚输入;S端子的C、Y信号分别经电容CD135,CD136耦合后从(71)、(72)脚输入;AV2的视频信号经电容CD129耦合后,从(73)脚输入;Cb、Y、Cr信号分别经LD21、CD139、CD123、RD111,CD128、LD28、CD138、CD132、RD21、LD22、CD141、CD140、RD122、CD130组成的滤波电路滤波后,从①~③脚输入。输入的视频信号经VPC323()D视频解码处理后,输出数字信号。

VPC3230D是一块总线控制型PAL/NTSC/SECAM制彩色电视信号处理集成电路,具有功能多、外围电路简单、性能优良等特点。VPC3230D(13)、(14)脚为总线控制端(SCL、SDA),与外围集成电路相连接;(15)脚外接的RD83、QD8、RDl04、DD6是一个复位控制电路,用于对芯片复位;(63)、(62)脚外接晶振XD1(20.25MHz),产生基准彩色所需信号。VPC3230D采用3.3V和5V供电。

VPC3230D(70)脚输出视频信号,经QD10、RD146组成的射随电路放大后,从QD10的发射极输出。VPC3230D(30)~(34)、(37)~(40)输出8bit的YC信号(简称8bit位格式的数字信号),送往FLI2300进行精密显像处理。

2.VGA及HDTV信号

VGA的RGB及Hs、Vs信号从端口JP5输入,VGA的RGB信号先由FB5~FB7、CD154、CD158、CD162滤波,再由QD4~QD6射随放大,最后送到P15V330(QD11)的②、⑤、(11)脚。

HDTV信号由端口JP4输入,HDTV的Y、Pb、Pr信号先由FB2~FB4滤波,再送入QD11的③、⑥、⑩脚。

P15V330是一个4通道2选1高性能视频模拟开关,具有导通电阻低、频带宽、低串扰等特点。VGA和HDTV信号经QD11切换后,从QD11的④、⑦、⑨脚输出RGB信号,经RD34、CD28、RD36、CD35、RD33、CD28电容耦合后,送到AD9883(uD3)(54)、(48)、(43)脚。

AD9883是ADI公司专为平板显示模拟前端接口设计的模数转换集成电路,采用80脚封装,3.3V供电电压。该IC内置三通道8位110MHz采样频率的AD转换器、同步处理器及时钟发生器、I2C主机接口等功能模块,其数字视频输出接口支持4:4:4的YUV信号输出。输入的YUV信号经AD9883处理后,从②~⑨脚、(12)~(19)脚、(70)~(77)脚输出8bit的数字YUV信号,分别送到FLI2300的(21)~(28)脚,(29)脚、(32)~(35)脚、(38)~(40)脚,(18)~(20)脚、(11)~(15)脚进行处理。AD9883的(30)、(31)脚是VGA的行同步和场同步信号输入端,(56)、(57)脚分别是SDA、SCL脚。AD9883的供电电压为3.3V,供电脚为(33)~(35)脚。

AD9883(67)脚(DATACK)输出数据时钟信号,(66)脚(HSOUT)输出行同步信号,(64)脚(VSOUT)输出场同步信号,(65)脚输出G复合同步信号,分别送到FLI2300④脚(IN-CLKl-PORTl)、①脚(HSYNCl-PORT1)和②脚(VSYNC-PORTI)。另外,AD9883(65)、(64)脚还分别与CPU(36)、(13)脚相连。