新型 FPGA 平台具有高度的灵活性和可扩展性,且集成度高,能够在单个或两个芯片上集成一个完整的异构动态运算系统。

自适应硬件在诸如导弹电子和软件无线电等功耗和系统尺寸有限,同时对环境高度敏感的应用中非常有用。采用动态重配置技术,可以在不增加系统功耗或电路板尺寸的情况下,实现支持不同应用模式的专用架构。传统解决方案侧重于控制部分,现在看来似乎已经不能有效地满足执行单元的数量及其异构性要求。只有采用兼具灵活性和可扩展性的分布式方案,才能够创建出面向未来的架构。

虽然这种技术潜力无限,但对整个业界来说,动态重配置的使用仍然有相当大的难度。工程师需要一种清晰明确的设计方式,既能够充分地发挥动态重配置的优势,又不影响应用描述,而且最重要的是,不增加开发成本。为了将动态性和高性能结合起来,我们建议采用基于多线程的执行模型对异构性进行抽象。开发人员可以将应用当作线程集来进行编程,而不必考虑线程是在标准处理器还是专用硬件上执行。在这种情况下,动态重配置的作用是进行线程优先调度(thread preemption)和上下文切换。由法国国家研究署 (French National Research Agency (ANR)) 赞助的 FOSFOR(灵活的可重配置平台操作系统)项目就专门负责开发这种新一代嵌入式、分布式实时操作系统。

1 FOSFOR 架构基础

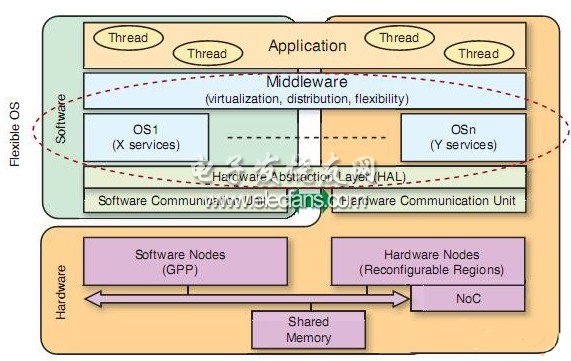

我们的目标是设计一种支持新的系统分区类型的架构,让软/硬件组件遵循同一执行模型。这就要求高度灵活的可扩展操作系统,能够为软件域和硬件域提供相似的接口。与传统方法不同,这种操作系统是完全分布式的,整个平台从应用的角度来看是同构的。这就意味着既能以静态方式,也能以动态方式在软件(处理器)或者硬件(可重配置单元)中部署应用线程,对分布式服务进行无差别的访问。

为了实现高效率,我们在紧邻可重配置区的硬件中实现操作系统服务。我们在异构操作系统内核之间实现了一个通信层,以确保从应用角度看服务是同构的。因此,将操作系统当作大量模块和执行单元部署在架构上,可以充分发挥虚拟化机制的优势,从而使应用线程在未预知任务的情况下运行和通信。

从编程人员的角度来看,该应用只是个线程集。我们可以利用赛灵思 FPGA 的动态重配置功能来提议这种硬件线程的新概念,同时也可采用与软件线程相同的方式来实现这一概念。我们的实现方式充分发挥了专用计算 IP 模块的性能优势。

除了要考虑到多处理器 SoC 中的执行单元,存储器结构还必须满足以下几项要求:应用线程需要的数据存储、每个线程执行上下文的存储以及线程间的数据交换。对于执行上下文的存储,我们认为有多种可能性。一种方式是集中存储执行上下文,这样为将其分配到不同执行单元提供介质。我们可以确认平台内的三种通信流:应用数据、控制信号和重配置/执行上下文。对于硬件线程之间的高带宽数据路径,我们使用专用的片上网络 (NoC)。

图1 通用 FOSFOR 架构

图中文字:

灵活的操作系统 软件 线程 应用 中间件(虚拟化、分布、灵活性) 操作系统 1(X 服务) 操作系统 n(Y 服务) 硬件抽象层 (HAL) 软件通信单元 硬件通信单元 硬件 软件节点 (GPP) 硬件节点(可重配置区域) 片上网络 共享存储器