摘要:针对信号发生器时输出频率精度高和幅值可调的要求,采用直接数字频率合成(DDS)技术,提出一种基于FPGA的幅值、频率均可调的、高分辨率、高稳定度的信号发生器设计方案。采用AT89S52单片机为控制器,控制FPGA产生波形的数字信号,结合双数模(D/A)转换器及低通滤波器,最终实现输出信号幅值0~5 V可调,分辨率为10 bits;频率范围1 Hz~10 MHz可调,最小分辨率为1 Hz;频率稳定度优于10-4。信号参数可通过键盘进行设置,并在LCD上输出。由于FPGA的可编程性,易于对系统进行升级和优化。

关键词:FPGA;信号发生器;DDS;单片机;VHDL

直接数字频率合成(DDS)技术具有相对频带宽、频率转换时间短、频率分辨率高、输出信号相位连续、能够实现全数字自动化控制等优点,已经逐步成为高性能信号发生器的核心技术。现场可编程门阵列(FPGA)器件具有工作速度快、集成度高、可靠性好和现场可编程等优点,在现代电子设备中的应用越来越广。

本文采用DDS技术和FPGA芯片设计了一种频率可调的信号发生器,可输出正弦波、方波、三角波和锯齿波等数字信号,其频率范围广,稳定性好,精度高,系统灵活,易于升级。

1 系统总体设计

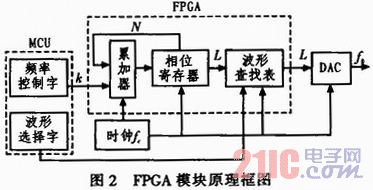

系统框图如图1所示,它由单片机控制模块、FPGA波形产生模块、幅度控制模块、数模转换(DAC)模块、低通滤波模块、键盘输入和液晶显示模块组成。FPGA模块采用DDS技术,可产生正弦波、方波、三角波或锯齿波的数字信号,经D/A转换、低通滤波后输出。其波形类型及频率大小通过单片机直接控制,输出信号幅度的控制由单片机通过幅度控制模块改变数模转换模块的参考电压来间接实现。

2 功能模块设计

2.1 FPGA模块

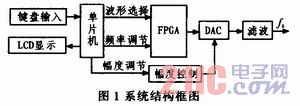

该模块根据MCU提供的频率控制字K及波形选择字,利用DDS技术产生波形数字信号,通过数模转换器DAC变成阶梯波,再经过低通滤波器平滑后就可以得到合成的信号波形。此模块主要由相位累加器、相位寄存器和波形查找表构成,其原理框图如图2所示。其中,fc为输入基准时钟频率,fo为输出信号频率,K、N、L分别为频率控制字、相位累加/寄存器、波形查找表和D/A转换器的字长。