图中相位累加器是核心,它主要由1个N位二进制累加器和1个由固定时钟控制的N位相位寄存器构成。相位寄存器的输出与累加器的一个输入端相连,MCU送来的频率控制字K加到累加器的另一个输入端。在每个时钟脉冲到达时,相位寄存器将其上一个时钟周期内的值送入累加器并与频率控制字K相加,其结果作为当前时钟周期的输出序列,此输出序列作为波形查找表的地址。波形查找表实质上是一个相位/幅度转换ROM电路,ROM内部存储了一个完整周期波形的相位/幅度值。相位寄存器每寻址一次波形查找表,就输出一个与相位对应的信号幅度值。频率控制字K决定了相应的相位增量,相位累加器则不断的对该相位增量进行线性累加,当累加器产生一次溢出时,就生成一个周期的DDS合成信号。

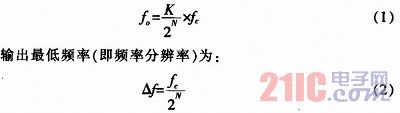

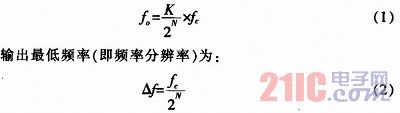

理想情况下,相位寄存器的N位全部用来寻址,这时DDS的合成频率为:

而DDS的最大输出频率由乃奎斯特采样定理决定,即FMax=fc/2。实际中DDS的最高输出频率由允许输出的杂散水平决定,一般取值为fo≤40%fc。因此,要改变DDS的输出频率,只要改变频率控制字K即可。

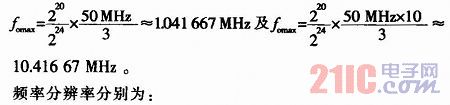

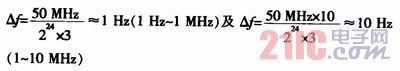

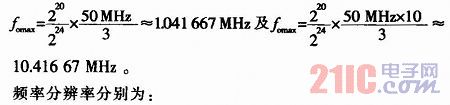

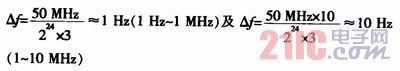

这里采用Altra公司的FPGA器件EP1C3T144C8,适合中规模应用,该模块设计由VHDL实现,后级采用10位D/A输出。为便于频率调节,根据式(1)和式(2),我们将输出频率分为两档(1Hz~1 MHz和1~10 MHz),并由FPGA根据键入的频率控制字自动选择。而两档输出的基准时钟fc由50 MHz晶振通过FPGA内部锁相环3分频得到(fc≈16.666 67 MHz),或者再经10倍频得到(fc≈166.666 7 MHz)。若相位累加器字长N为24位,频率控制字K为20位二进制数,则两档输出的最高频率分别为:

可见,即使在输出最高频率时,也能保证每周期波形有16个点,从而有效保证了输出信号波形的逼真度。

将波形数据存储在波形ROM中的方案有2种:一种是在一个完整周期内进行采样,然后将采样值依次存于ROM单元中,这个方案的优点是思路清晰,实现简单;另一种方案是根据周期信号波形的对称性,只对其在1/2或1/4周期上采样并存储,因此可以节省存储空间,但实现上要复杂些。为简化设计,本文采用了第一种方案。

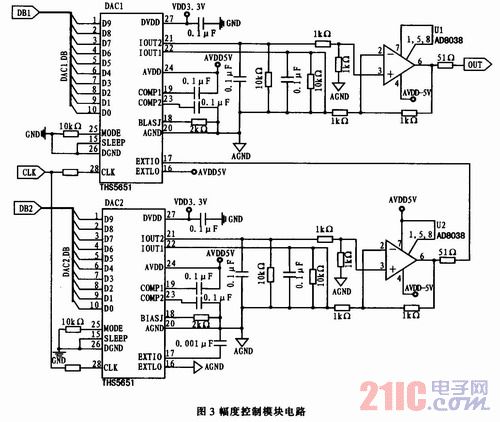

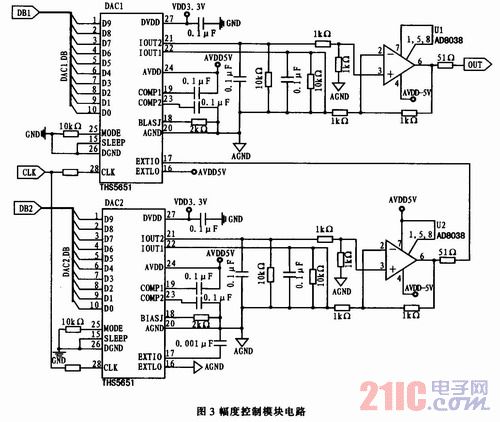

2.2 幅度控制模块

输出信号的幅度控制是通过2片DAC芯片实现的,其电路图如图3所示。其中,第1片DAC用来将FPGA输出的波形的数字信号转换为模拟阶梯信号,幅值的调节是通过第2片DAC的输出改变第1片DAC的参考电压来实现。

上一页 [1] [2] [3] 下一页