当FPGA vi开始运行时,从Host vi读取数据的FIFO需要一定的初始化时间,时间长度与FIFO的深度成正比。在初始化期间FIFO输出一系列的无效默认值。为了不让无效值进入到下一级的运算中,在DMA方式的FIFO之前加了一个FIFO函数——Get Number of Element to Read,该函数用于获得FIFO内有效数据的数量。当有效数据的数量大于0时,再开始进行下一级运算。考虑到FPGA有限的硬件资源和FPGA FIFO最小

值的限制,将数据的地址宽度设为M=11,根据上文分析DMA FIFO的深度设为2M+5=2 053 KB。

4.2 主控计算机程序设计

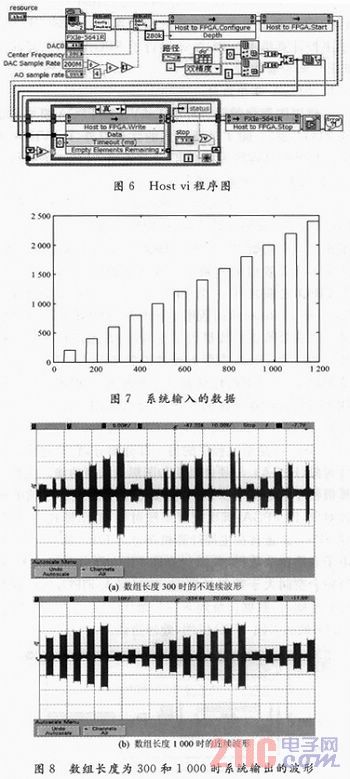

Host vi是系统程序的另一部分部分,它具有建立硬件对象(FPGA)、与硬件通信和图形显示等功能。主控计算机程序图如图6所示,首先要建立与之进行通信的硬件对象,即FPGA;其次配置系统时钟、输出模式;再次创建FIFO,设置其在主控计算机部分的FIFO深度;然后从电子表格读取数据,并循环查询FIFO剩余空间的大小,当剩余空间大于数组长度时,数据写入FIFO当没有足够的空间时,数据保留到下一个循环,满足条件后再写入FIFO;最后关闭FIFO应用,处理错误。

当输入数组长度分别为300和1 000,形状如图7所示的波形时,输出数据的波形如图8所示。由于AD9857上变频的原因,使得输出波形在输入的矩形包络中带有载波,载波频率为60 MHz。根据表1中的数据可以得出结论:此处的编程和上述实验的结果是一致的,即FPGA输出频率为10 MHz,数组长度大于500时,系统数据的输出是连续。同时此结果也表明本文中的LabVIEW程序实现了数据的连续传输。

5 结语

在使用LabVIEW FPGA模块和NI公司的RIO设备设计中频信号生成系统时,FPGA收发数据的速率不同造成了数据传输的不连续,设定合适的FIFO深度可以有效解决该问题。本文根据DMA FIFO的工作原理,确定了给FIFO两个部分分别设定合适深度的方法。通过设定合适的FIFO深度,实现了数据的连续传输,为后续的工程设计奠定了基础。该设定FIFO深度的方法也对其他使用LabVIEW FPGA模块的工程设计具有一定的参考价值。