发送模块由发送控制进程、写数据进程、并/串转换进程、状态操作进程等进程构成。其中,最主要的是发送控制进程,在发送控制进程中声明了一个6比特的变量scit_v,由它的取值(状态机)状态来控制整个发送过程。scit_v被分为高四位的sh_t和低两位的sl_,tscit_v在系统复位后被赋初值28(011100B),每来一个时钟scit_v增量,每来四个时钟sh_t增量,当sh_t为0111B时发送起始位,sh_t为1000~1111B时发送8比特的数据。下面给出的是发送控制进程和发送接收数据进程的原代码:

-----数据发送控制进程-----

PROCESS(clk,reset)

variablescit_v:integerrange0to63;

variablescit_s:std_logIC_vector(tdownto0);

BEGIN

IF(reset=0')'THEN

scit_v:=0;--"000000"

ELSIF(clkE'VENTANDclk=1')'THEN

IF(scit_v<=27)THEN

IF(tdEMPTY_s=0''ANDwr=1')'THEN

scit_v:=28;--sci_v="011100"

ELSE

scit_v:=0;

ENDIF;

ELSE

scit_v:=scit_v+1;

ENDIF;

ENDIF;

scit_s:=conv_std_logic_vector(scit_v,6);

scit<=TO_STDULOGICVECTOR(scit_s);

ENDPROCESS;

------数据的串行发送-----

PROCESS(sh_t)

BEGIN

CASEsh_tIS

WHEN"0111"=>txd<=0';'

WHEN"1000"=>txd<=din_latch(0);

WHEN"1001"=>txd<=din_latch(1);

WHEN"1010"=>txd<=din_latch(2);

WHEN"1011"=>txd<=din_latch(3);

WHEN"1100"=>txd<=din_latch(4);

WHEN"1101"=>txd<=din_latch(5);

WHEN"1110"=>txd<=din_latch(6);

WHEN"1111"=>txd<=din_latch(7);

WHENOTHERS=>txd<=1';'

ENDCASE;

ENDPROCESS;

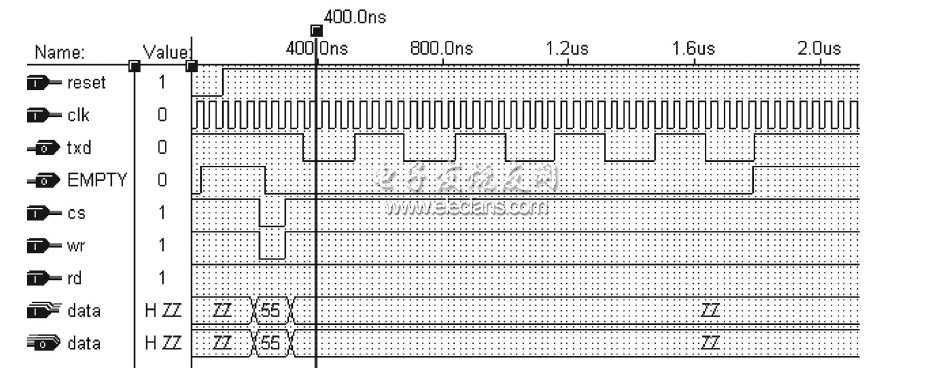

图3给出的是发送数据的仿真图。当CS和WR有效时写入数据55H,同时EMPTY被置成无效状态,开始数据的发送,从图中可以看到TXD上电平的变化过程,当发送结束后EMPTY变为有效。

图3 发送数据的仿真波形