由于重构后每个信号路径上都没有负延时情况,根据时序重构原理的性质,则这个重构映射是合理的,重构后的算法结构是合理的,稳定的。可以看到,合理地选取映射规则对电路进行时序重构,可以合理地斩断关键路径,提高系统运行速度。在这里,重构后的关键路径为一个处理单位。同理,可以对多级格型预测器模块进行时序重构。同样的,重构后格型预测器电路的关键路径也为一个处理单元。这样,整个改进后的RD-GALJP(Retimed Delay-GALJP)系统结构的关键路径就缩短为1个处理单元。

3 基于FPGA的算法的实现与仿真

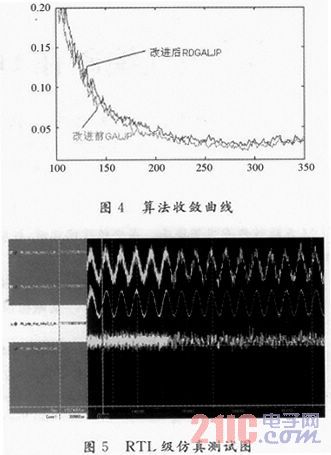

以自适应噪声对消为模型进行仿真验证,设格型预测器的反射系数收敛因子为0.008,期望响应估计器的收敛因子为0.002。在Matlab中对改进前和改进后的算法进行仿真,测试信号为随机2FSK+高斯白噪声,SNR=-9 dB,得到的收敛曲线如图4所示。

可以看到,改进后的算法在收敛性能和稳态表现都有些许下降,但是降低的幅度很小,在可接受的范围内。利用DSP-builder进行FPGA算法建模,实现4阶16位定点格式的格型滤波结构,并在Modelsim中进行RTL级仿真,得到的改进算法滤波效果如图5所示。

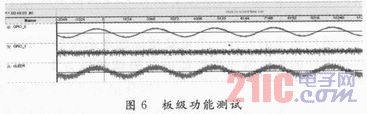

在EP2C70F896C6芯片上进行代码的综合,得到的结果为:改进前系统的最高工作频率为23.99MHz,改进后系统的最高工作频率为167. 53 MHz。显然,系统频率在算法结构改进后有很大的提高。最后,利用DDS技术产生需要的测试信号和噪声(测试频率为100 MHz),将相应的HDL代码综合布线后下载到FPGA芯片中,利用Signaltap内嵌逻辑分析仪进行板级功能测试,结果如图6所示。

实验结果表明,该模块可以很好地运行在100 MHz以上,适用于高速自适应处理的场合。

4 结 语

FPGA以其高效的硬件特性在信号处理方面有着越来越多的应用。本文结合驰豫超前流水线和时序重构技术,提出一种RD-GALJP算法结构,并以自适应噪声对消为模型进行算法仿真。算法仿真的结果表明,改进算法结构相比改进前的算法在滤波性能上只有些许下降,但是却能够很好地切割关键路径,以利于流水实现。最后以4阶16位定点格式为背景在FPGA中对算法进行实现和板级功能测试,综合布线后得到16 7.53 MHz采样吞吐率的运算性能,比较于改进前的23.99 MHz的工作频率表明,工作频率的改善显著。实验结果表明,改进算法结构可以很好地应用于对输入自相关矩阵特征值扩散敏感的高速高灵敏度的自适应信号处理场合。