处理交流信号时,digiPOT的性能受带宽和失真的限制。受寄生器件影响,带宽是指在小于3 dB衰减时能够通过digiPOT的最大频率。总谐波失真 (THD)(此处定义为后四个谐波的rms之和与输出基波值的比值)是信号通过器件时衰减的量度。这些规格涉及的性能限制由内部digiPOT架构决定。通过分析,我们可以更好地全面了解这些规格,减少其负面

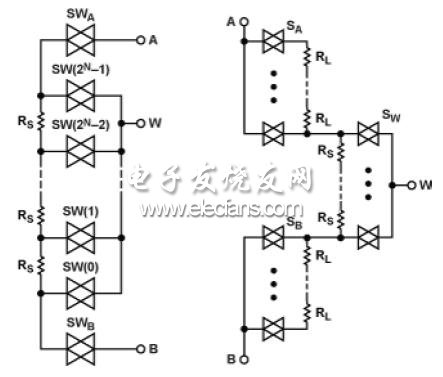

内部架构已从传统的串联电阻阵列(如图6a所示)发展至分段式架构(如图6b所示)。主要的改进是减少了所需内部开关的数量。第一种情况采用串行拓扑结构,开关数量为N = 2n是分辨率的位数。 n = 10, 时,需要1024个开关

图6. a)传统架构,b)分段式架构

专有(专利)分段式架构采用级联连接,可以最大限度地减少开关总数。图6b的例子显示的是两段式架构,由两种类型的模块组成,即左侧的MSB和右侧的LSB。

左侧上下模块是一串用于粗调位数的开关(MSB段)。右侧模块是一串用于精调位数的开关(LSB段)。MSB开关粗调后接近RA/RB比。LSB串的总电阻等于MSB串中的单个阻性元件,LSB开关可对主开关串上的任一点进行比率精调。A和B MSB开关为互补码。

分段式架构的开关数量为:

N = 2m + 1 + 2n – m,

其中n是总位数,m是MSB字的分辨率位数。例如n = 10 and m = 5, 则需要96个开关。

分段式方案需要的开关数少于传统开关串:

两者相差的开关数 = 2n – (2m + 1 + 2n – m)

在该例中,节省的数量为

1024 – 96 = 928!

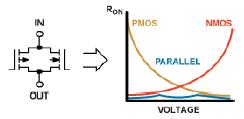

两种架构都必须选择不同电阻值的开关,充分考虑到模拟开关中的交流误差源。这些CMOS(互补金属氧化物半导体)开关由并行P沟道和N沟道MOSFET构成。这种基本双向开关可以保持相当恒定的电阻(RON) 信号可达完整的供电轨.

带宽

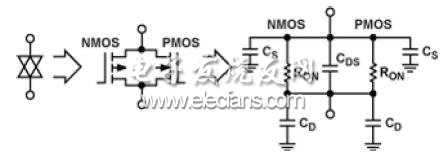

图7显示的是影响CMOS开关交流性能的寄生器件.

图7.CMOS开关模式.

CDS = 漏极-源级电容; CD = 漏极-栅级 + 漏极-体电容; CS = 源级-栅级 + 源级-体电容.

传递关系如以下公式定义,其中包含的假设为:

源阻抗为 0

无外部负载影响

无来自CDS的影响

RLSB << RMSB

其中:

RDAC是设定电阻

RPOT是端对端电阻

CDLSB是LSB段的总漏极-栅级 + 漏极-体电容

CSLSB是LSB段的总源级-栅级 + 源级-体电容

CDMSB是MSB开关的漏极-栅级 + 漏极-体电容

CSMSB是MSB开关的源级-栅级 + 源级-体电容

moff是信号MSB路径的断开开关数量

mon是信号MSB路径的接通开关数量

传递公式受各种因素影响,与代码存在一定关联,因此我们采用以下额外假设来简化公式

CDMSB + CSMSB = CDSMSB

CDLSB + CSLSB >> CDSMSB

(CDLSB + CSLSB) = CW (详见数据手册)

The CDS对传递公式没有影响,但由于其出现的频率通常比极点高的多RC 低通滤波器是主要的响应。理想的近似简化公式为:

带宽(BW)定义为:

其中CL是负载电容.

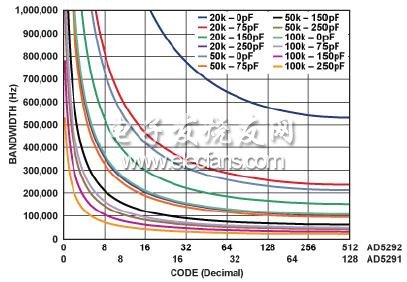

The BW与代码有关,最差的情况是代码在半量程时,AD5292的数字值为29= 512,AD5291的数字值为27 = 128 (见目录). 图8显示的是低通滤波效应,它受代码影响,在不同标称电阻与负载电容值时会发生变化.

图8.各种电阻值的最大带宽与负载电容

PC板的寄生走线电容也应加以考虑,否则最大带宽会低于预期值,走线电容可以采用以下公式简单计算:

其中

&epSILon;R是板材的介电常数

A是走线区域(cm2)

d是层间距(cm)

如,假设FR4板材有两个信号层和电源/接地层, εR = 4, 走线长度 = 3 cm宽度 = 1.2 mm, 层间距 = 0.3 mm; t则总走线电容约为 4 pF.

失真

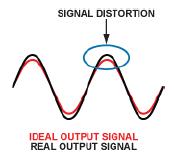

THD用于量化器件作为衰减器的非线性。该非线性由内部开关及其随电压变化的导通电阻 RON而产生。图9所示为放大的幅度失真示例.

图9.失真

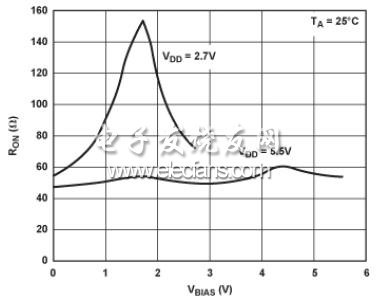

与单个内部无源电阻相比,开关的RON很小,其在信号范围内的变化则更小。图10显示的是典型的导通电阻特性。

图10.CMOS电阻

电阻曲线取决于电源电压轨,电源电压最大时,内部开关的RON 变化最小。电源电压降低时,RON 变化和非线性都会随之增加。图11对比了低压digiPOT在两种供电电平下的 RON