软件设计部分主要包括以下四部分:

·初始化:对变量参数、系统时钟、PIE、EV、Flash、GPIO等进行配置。

·中断模块:SCI中断和定时器T2、T3上溢中断。

·数据处理模块:分段+取算术平均值。

·输出操作模块:数据经RS-232传给上位机。

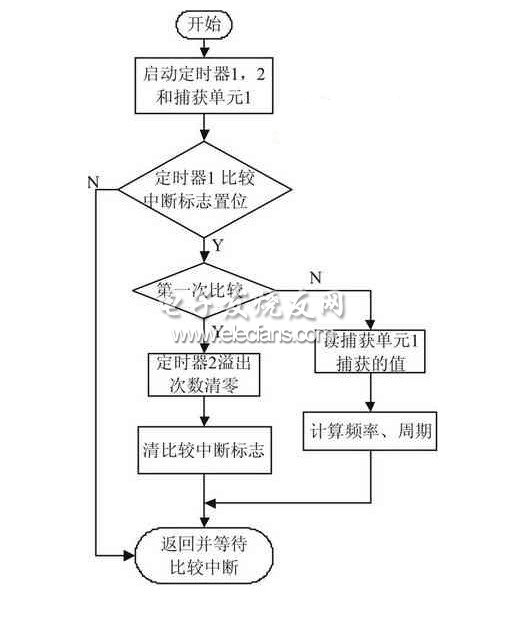

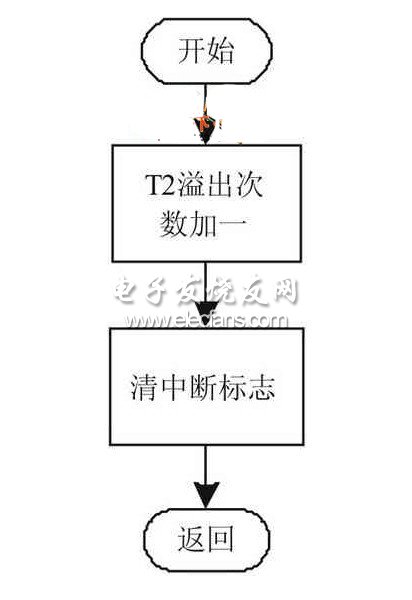

图5为测频率、周期软件流程图,图6为定时器2的溢出中断流程图。

图5 测频率、周期流程图

图6 定时器T2溢出中断流程图

在该部分初始化时,要进行以下配置:通用定时器T1时钟输入为外部定时器时钟,通用定时器T2时钟输入为内部时钟输入,用来对标准脉冲进行计数,该标准脉冲由外部30MHz的有源晶振提供;捕获单元1设置为上升沿捕获,用来捕获T1PWM引脚输出PWM波的上升沿,在每次比较匹配时读取定时器T2的计数值T2CNT,该值保存在CAP1FIFO内。初始化时要将捕获单元1的状态寄存器中的FIFO堆栈状态设置成空堆栈;将定时器T1的定时周期设置为4个被测信号的周期长度,通过测得的定时器T1的一个定时周期内的标准脉冲的个数,计算出被测信号频率,然后对被测信号进行分段,分别为低频段(小于46.875Hz),中频段(大于46.875Hz,小于2343.75KHz),以及高频段(大于2343.75 KHz),其中分段的依据是定时器的计数饱和值为65536和计数个数应大于等于1。若信号频率为中高频段则重新配置定时器T1,定时器T2的寄存器,来改变定时周期以及每个门闸时间内的高频填充脉冲的个数。在定时器T1的下一个定时周期内计算出频率和周期。另外,定时器T2的溢出次数要在第一次发生比较匹配时清零,而是否是第一次发生比较匹配则通过设置一个标志来判断。当溢出次数清零后才开始记溢出次数,直到第二次发生比较匹配。

下一步改进意见

该方法的测量误差主要来自硬件部分,整形电路的优劣直接关系到测量精度的高低。所以我们下一步的工作就是改进整形电路的整形效果和抗干扰性能,尽最大可能减小信号整形带来的误差。

由于DSP定时器在计数时存在计数饱和的情况,因此在实现该等精度测量时存在上限,即当被测信号频率高于高频填充脉冲的频率时,该方法就不能实现等精度了。可以在该方案的基础上进行以下处理:选择定时器T1定时周期内被测信号的个数固定,可设置T1PR为65529,同时将定时器T2的时钟修改为75MHz,这样就能保证每个门闸时间内高频填充脉冲的个数,从而在对高频信号实现频率和周期测量时保证了精度。

但选择定时器T1时钟输入为外部时钟时对被测信号的输入范围存在限制,如果要进一步提高测量的信号的范围,使得范围达到上百兆或上G赫兹,可以考虑相位测量的方法,将被测信号设为360度,根据被测信号与标准信号之间的X度相位差,计算被测信号频率。