大多数模拟接口可以利用驱动放大器之后的LC抗混叠滤波器来设计。输入频率使得系统可以作为集总元件电路进行分析,而不涉及到阻抗匹配问题。只要信号路径距离小于模拟输入波长的1/10,集总元件模型就是充分有效的。即使信号路径距离较长,通常也不要求阻抗匹配。然而,较长的信号路径距离会带来其他问题。

板走线路径会将寄生电感和电容引入LC滤波器。这可以通过滤波器设计来处理,即改变滤波器元件值,以补偿印刷电路板(PCB)的寄生效应。关键问题是要让抗混叠滤波器的最终并联电容尽可能靠近ADC输入端,从而使采样网络中的电感最小,以免因为模拟接口的时钟性质而引起响铃振荡。

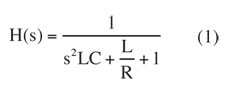

为了说明这一点,考虑一个简单的二阶LC AAF设计,它包括一个串联电感、并联电容和端接电阻,因而该滤波器部分的传递函数如下:

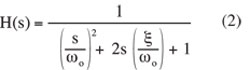

其通用二阶形式为:

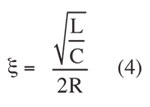

如果让这两个传递函数的系数相等,可以得到:

并且:

对于大多数应用,带宽和滤波器类型是固定的设计参数(本例为巴特沃兹型)。单凭这两个参数并不能确定滤波器设计,最终的决定参数是阻抗水平,即滤波器的阻抗可以调整,以便有利于ADC驱动或放大器负载。

假设带宽为200 MHz,滤波器类型为二阶巴特沃兹响应。放大器设计驱动150 Ω负载,因此R = 150 Ω、L = 155 nH、C = 4 pF。然而,如果4 pF并联电容不足以缓冲电荷反冲,则可以加大放大器的负载为代价,降低AAF阻抗,反之亦然。

从实际考虑,AAF设计还存在其他限制,如电路板物理布局布线等。例如,有时可能无法让放大器与ADC靠得非常近,这样一来,电路板布线就成为AAF设计的一部分。走线路径会增加额外的串联电感和电容,从而影响滤波器的响应。

这可以通过选择适当的元件来处理,即降低电感值,让电路板走线来补偿实际的AAF电感值。这样,设计的最重要部分就是在不违背制造规则的前提下,让并联电容尽可能靠近ADC输入端,因为该电容要“缓冲”电荷反冲(参见下图)。

长走线的等效电路实际上会反映一些寄生电感。考虑上面的等效电路,它看起来像是一个不同的RLC模型。因此,这里的目标是尽量降低电路中的额外走线电感“L”,从而使可能发生的反冲响铃振荡最小,以免产生失真和/或不同的滤波器曲线。这只是一个例子,说明放大器、AAF和ADC需要紧密配合才能使信号链有效工作。

结束语

高速ADC无论采用缓冲式架构,还是采用无缓冲式架构,都有各自的理由。无缓冲型高速ADC可能需要更复杂的模拟接口设计,但就功耗而言,它可以给整体系统效率带来很大的好处。无缓冲型ADC设计要求将模拟接口设计与采样网络作为一个整体考虑,包括放大器、AAF和ADC的内部采样网络。对于大多数应用,只要认真考虑上述变量,就可以圆满完成任务。