本系统所选用的G.728标准的语音编码算法需要8kHz的采样速率,所以这里我们对ADC和DAC要求就是最高采样率或转换时间不低于8kHz。

根据语音信号的特点,我们选用TI公司的TLC32044芯片,这是一片集成了ADC和DAC功能的芯片。它的最高转化速率为19.2kHz,转换位数为14位,输入电压带范围可调,有标准同步串口,还有输入滤波器和输出重构滤波器,这样可以省去模拟滤波器的设计。TMS320VC5409与TLC32044的接口电路如图3所示。

图3 DSP与DAC、ADC的接口电路

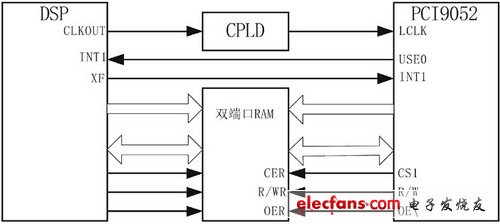

图4 DSP与双端口RAM的接口电路

图5 PC19025双端口RAM接口电路

DSP与双端口RAM之间的通信

为了体现PCI总线速度快的优点,我们选用速度较快的双端口RAM CY7C133-25,最大传输速率为25ns。双端口RAM在DSP的数据空间的地址映射为8000H-87FFH。

这里需要强调的是双端口RAM的BUSY信号。我们并不使用这个信号,因为我们分别对双端口RAM的不同部分进行操作,所以避免了可能发生的任何冲突,因此省去了BUSY信号,BUSY信号悬空。电路的电压转换和地址译码同样由CPLD来完成。

PCI9052与双端口RAM之间的通信

DSP的任务是完成语音的编码和解码,然后再通过PCI总线与计算机进行数据交换。这里我们使用了PCI接口芯片PCI9052。所以,问题就变成了DSP与PCI9052之间的通信。DSP与PCI9052之间用一片双端口RAM(容量为2k×16bit)进行数据交换。

由于PCI9052具有5个局部地址空间和4个局部设备片选信号,所以连线变得相当简单,我们只需要将双端口RAM映射到其中一个局部地址空间,然后使用其中的一个片选信号连接到双端口RAM的,最后将PCI9052的读写信号(R/W)和对应连接到双端口RAM的R/W和。这样就省去了地址译码等外围逻辑电路。

软件系统设计

IP电话系统要实

现的算法就是语音编码算法,还要完成与计算机的数据交换。软件部分的主要作用是用嵌入式操作系统中的TCP/IP协议对需要传送的语音编码信号进行打包,再通过计算机上的网卡将数据通过Internet传送到接收方,并把接收到的TCP/IP包还原为原来的语音编码信号,最后通过PCI总线传输给DSP进行语音解码。

结语

实践证明,本系统设计方案的主要优点是对计算机硬件的要求不高,处理速度快,语音的输入输出系统单独集成,信噪比(SNR)高,具有相当的适用和推广价值。