Freescale构建了一个多芯片系统的原型,其中包括一个双核MXC2基带处理器和一个RF收发器芯片的数字部分。基带处理器内置一个用于调制解调器处理的Freescale StarCore DSP内核、一个用于用户应用处理的ARM 926内核,以及 60多个外设。

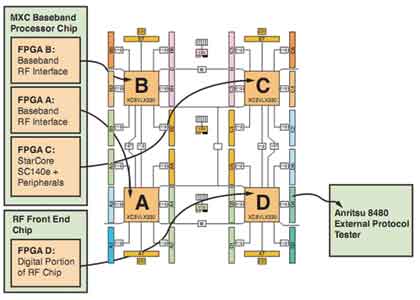

Synopsys HAPS-54原型板用来实现原型(如图3所示)。该基带处理器有500多万个ASIC门,Scott的团队使用Synopsys Certify工具将其在原型板上划分给3个赛灵思Virtex-5 FPGA,同时把数字RF设计布置在第四个FPGA中。Freescale 决定不构建模拟部分的原型,而是直接从Antritsu协议测试盒中以数字形式提供移动网络数据。

图3 Freescale的SoC设计在HAPS-54原型板上的分区

较早的内核使用的某些设计技术对ASIC来说非常有效果,但对FPGA来说却不太好用。另外,RTL的一部分是从系统级设计代码中自动生成的,由于其过于复杂的时钟网络,对FPGA来说也是相当不利的。因此,必须对RTL进行一些调整,使其更加兼容FPGA,这样做的成效非常显著。

仅在完成首个芯片后一个月,Freescale团队就成功地从这个系统中拨出了第一个移动电话呼叫,把产品开发进度缩短了6个多月,这非常具有里程碑式的意义。

这个例子说明基于 FPGA的原型方法能够给软件开发团队提供什么样的增值工具,能够在产品质量和项目进程方面带来怎样显著的回报。

接口优势:测试真实条件下的数据效应

很难想象有这样一种 SoC 设计可以不遵守输入数据、处理数据、生成输出数据的基本结构。实际上,如果我们深入SoC设计,就会发现无数的子模块遵循着同样的结构,直到单个门级。

要在这些层级中的每一个层级验证正确的处理,要求我们提供完整的输入数据集,并观察处理结果的输出数据是否正确。对单个门来说,这个工作很简单,对小型 RTL 模块来说,也是可能的。但随着系统日趋复杂,从统计上来说基本没有可能确保输入数据和初始条件的完整性,尤其是在有软件运行在一个以上的处理器的时候。

最后一点非常重要,因为不可预测的输入数据能扰乱所有的SoC系统,即便是精心设计的关键SoC设计也难以幸免。与新输入的数据或者输入数据不寻常的组合或序列相结合的,是非常多的SoC 可能的前置状态,可能会使SoC处于某种无法验证的状态。当然,这种情况不一定是什么问题,SoC可以在无需系统的其他部分干预的情况下恢复,或者用户根本就没有察觉。

但是,不能验证的状态必须在最终芯片中避免,因此我们需要尽可能全面地测试设计的方法。在设计的功能仿真过程中,验证工程师会采用有力的方法,比如受约束随机激励和高级测试工具来完成多种测试,旨在达到可接受的测试覆盖面。但是,完整性仍受验证工程师选择的方向和给定的约束条件的限制,并受限于可用于运行仿真的时间。结果虽然受约束随机验证永远不可能穷尽,但能够大大增强我们已经测试了所有输入的组合(包括可能的输入和极端情况输入)的信心。

对实验室可行性实验的优势

在项目的初始阶段,需要对芯片拓扑、性能、功耗以及片上通信结构做出基本决策。部分决策采用算法或系统级建模工具便可良好执行,但也可以采用 FPGA 进行某些额外的实验。这是否是真正基于FPGA的原型设计呢?我们正使用 FPGA进行某个概念的原型设计,但这与使用算法或数学工具不同,因为我们需要某些可能是由这些高级工具生成的 RTL。一旦进入FPGA,就可采集早期信息帮助推进算法和最终SoC架构的优化。基于FPGA的原型为项目该阶段带来的优势是,可使用更准确的模型,而且这些模型的运行速度非常快,能够与实时输入互动。

这种类型的实验性原型值得一提,因为它们是在全面的SoC项目中使用基于FPGA的原型设计硬件和工具的又一途径,可为我们的投资带来更高的回报。

在实验室外使用原型

基于FPGA的原型设计可用于验证SoC设计的一个真正独到之处,是其独立工作的能力。这是因为FPGA可通过闪存EEPROM卡或其他独立介质进行配置,无须主机PC管理。因此该原型不但可独立运行,而且还可用于各种环境下的SoC设计测试,这与其他建模技术(如需要依赖主机干预的仿真)提供的环境俨然不同。

在极端情况下,原型可以完全从实验室中取出,用于现场真实环境中。比如将原型安装在开动的车辆上,研究设计对外部噪声、移动、天线场强等条件变化的依赖性。比如,本文作者就曾将移动电话的基带原型安装在车辆上,通过公共GSM网络在移动中拨打电话。

芯片架构师与其他产品专家需要与早期客户互动,展示其算法的重要特性。基于FPGA的原型设计在项目极早期的这个阶段可能是非常关键的优势,但这种方法与主流SoC原型设计略有不同。

基于FPGA原型的不足

我们撰写本文的目的是公正地看待基于FPGA的原型的优势与局限性,因此在前面谈及各种优势之后,我们将在下面介绍部分局限性。

首先最重要的是,FPGA原型不是RTL模拟器。如果我们的目的是编写一些RTL,然后尽快在FPGA中实施,以查看它是否能工作,那么我们应该重新思考所忽略的东西。FPGA对运行RTL“模型”来说确实是一种速度更快的引擎,但当我们开始设置该模型的时候,速度优势就会大打折扣。此外,模拟器的仪表盘部分能够完整地控制激励和掌握结果。我们应该思考仪表化FPGA的方法,深入了解设计的功能性,但即便是在这方面最完善的设计,也只能提供一部分真正能用于 RTL 模拟器仪表盘的信息。因此,该模拟器是用于重复编写和评估RTL代码更加理想的环境,因此我们应该等到模拟基本完成后,RTL相当成熟后才能将其交付给FPGA原型设计团队。

基于FPGA的原型不是ESL

Synopsys的Innovator或Synphony等电子系统级(ESL)工具或算法工具可在SystEMC中完成设计,或通过预定义模型库进行构建。然后,我们不但可在相同的工具中模拟这些设计,而且还可深入了解其系统级性能,包括运行软件,在项目初期阶段进行软硬件权衡。

使用基于FPGA的原型方法,我们需要RTL,因此它不太适合研究算法或架构,因为这两者通常不采用RTL方式表达。对软件来说,FPGA原型设计的优势是在当 RTL 成熟得可以构建硬件平台的时候,软件可在更加准确以及更加真实的环境中运行。对那些具有天马行空想法的人来说,可以编写少量RTL在FPGA上运行,进行可行性研究。这是一种极少而又非常重要的FPGA原型设计的使用方法,但别把它和整个SoC的系统级或算法研究混淆在一起。

持续性是关键

优秀的工程师往往会为其工作选择适当的工具,但应该随时有一种方法可以将半成品交给他人继续完成。我们应该能够在尽量不增加工作量的情况下,将来自ESL模拟的设计移交给基于FPGA的原型。此外,部分ESL工具还可通过高层次综合实现设计,生成RTL供SoC项目整体使用。基于FPGA的原型能够接收该RTL,并以高周期精度在电路板上运行。但我们需要再次等到RTL相对稳定下来,这需要等到项目软硬件分区和架构研究阶段完成后。

采用FPGA进行原型设计的原因

当前SoC是从算法研究人员到硬件设计人员,乃至软件工程师和芯片布局团队等众多专家的工作结晶,在项目不断发展的同时,各类专家也都有自己的需求。SoC项目的成功很大程度上取决于上述各类专家所使用的硬件验证、软硬件联合验证以及软件验证的方法,基于FPGA的原型设计可为每一类专家带来各种不同的优势。

对于硬件团队而言,验证工具的速度可对验证吞吐量产生巨大的影响。因此一些团队采用基于FPGA的原型为这种硬件测试提供具有更高性能的平台。例如,我们可以在近乎实时的条件下运行整个操作系统的引导程序,节省需要花上数天才能达到相同目的的模拟时间。

对于软件开发团队而言,基于FPGA的原型可为目标芯片提供独特的流片前模型,能够在开发接近尾声时高速、高度准确地进行软件调试。

对于整个团队而言,SoC项目的关键阶段是在软硬件初次结合的时候。硬件将由最终软件执行,而执行方式可能是单纯硬件验证方案难以预见或预测的,从而最终将出现新的硬件问题。这在多核系统中或者在那些运行同步实时应用的系统中特别普遍。如果这种软硬件的采用要等到第一个器件制造完毕后,那么毫不夸张地说,到那时再发现新的缺陷就不太好了。