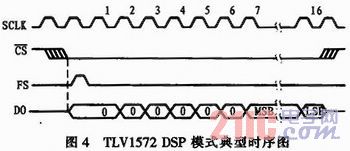

TLV1572有2种工作模式,即DSP模式和微控制器模式,这2种工作模式是由它的P3(帧同步输入信号)的电平决定的,FS引脚连接电源VCC,一直为高电平,则TLV1572工作在微控制器工作模式下;如果TLV1572在DSP工作模式下,则FS引脚或者由TMS320 DSP的MCBSP的帧同步信号(FSR)提供,或者由系统外部引入。

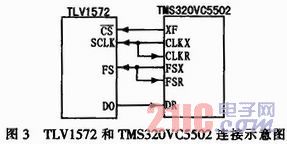

1.4 TLV1572与DSP的McBSP缓冲串口的连接

TLV1572与TMS320VC5502 DSP串口连接如图3所示。

TLV1572工作在DSP模式下,其典型时序图如图4所示。

在DSP模式下工作时,当TLV1572 A/D的片选信号/CS变低时,FS也必须为低,而且为了确保TLV1572的DSP模式的正确锁定,FS信号电平要被检测2次,一次是在/CS下降沿时检测FS电平(也就是对于/CS下降沿的FS建立时间,最小6 ns),一次是紧接其后的相对于/CS下降沿来说的一个内部延迟检测(也就是对于/CS下降沿的FS保持时间,最小为9 ns)。综上所述,为了保证TLV1572能正确锁定在DSP模式下,在/CS变低后FS要至少维持15ns的时间。

在确保TLV1572工作在DSP模式下后,也就是FS的低电平至少要维持15 ns的时间后,TLV1572 A/D要在每一个SCLK时钟信号的下降沿检测FS的电平状态,一旦FS变高,说明A/D进入复位状态,之后当FS变低时,TLV1572等待DSP锁存第一个0。这里,FS的上升沿对于对SCLK的下降沿来说有一个FS的建立时间(至少10 ns),然后相对应这个SCLK的下降沿,FS有一个保持时间(至少要4 ns)。满足至少上述的14 ns后,FS才能变低。

采样从FS变低后的第一个SCLK的下降沿开始,一直到输出第6个0时的那个SCLK的上升沿,在这个SCLK的上升沿,开始转换并输出相应转换的数据,这里有1 bit的延迟,而DSP对转换数据的采样发生在SCLK的下降沿。经TLV1572转换的数据前导有6个0,之后才是转换的由高位到低位的10 bit数据输出。也就是说TLV1572对一次的数据完整转换需要16个SCLK。如果在第16个SCLK时钟的下降沿检测到FS变高了,则在即后的下一个SCLK,也就是第17个SCLK开始下一次的新的数据的采样与转换,这样就实现了TLV1572的对数据的连续转换。

2 软件构成

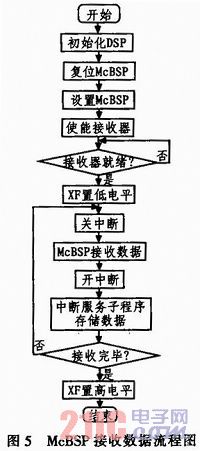

当所传输的信号从TLV1572的模拟信号输入端输入后,TLV1572再对输入的信号进行采样,并将采样后的数据传送到DSP。程序主要包括初始化DSP和缓冲串口McBSP,将McBSP配置为接收器,包括复位MeBSP的接收器,根据需要对McBSP的寄存器编程,使能接收器,启动A/D,采集数据并存储,其流程如图5所示。