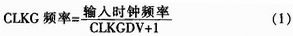

在对DSP的McBSP进行操作时,McBSP的内部采样率发生器的输出时钟CLKG驱动给CLKR,CLKR同时提供给A/D的SCLK。而McBSP的采样率发生器的时钟源(CLKSRG)由CPU提供的,对CPU时钟进行分频以产生CLKG。由于CPU的时钟极性总为正,因此CPU时钟信号的上升沿产生CLKG的上升沿。对采样率发生器的寄存器编程后,要等待2个CLKSRG(时钟源)周期以确保内部同步。当采样率发生器使能后,要等待2个CLKC周期,以保证采样率发生器稳定工作。在CLKSRG的下一个上升沿,CLKRG变为1,启动频率如式(1)所示的时钟。

帧同步信号(内部FSR),对于串口来说,都是内部信号,都是高电平有效。如果将串口配置成外部帧同步(FSR输入到McBSP),且FSRP=1(接收帧同步信号低有效),则外部低电平有效的信号在送给接收器(内部FSR)之前要做转换。当McBSP的FSR为输入时,McBSP在CLKR的下降沿检测这个FSR信号。到达DR引脚的接收数据,也在内部CLKR的下降沿采样。这里的内部时钟CLKR是由采样率发生器时钟(CLKG)驱动,内部送给McBSP。

接收器可以在时钟的上升沿可靠的对输入数据进行采样。接收时钟的极性(CLKRP)设置成采样接受数据所用的沿。注意:McBSP总是在内部CLKR的下降沿对数据采样,因此如果CLKRP=1,且选择内部时钟(CLKRM=1),则内部下降沿触发的时钟,在送给CLKR引脚输出之前,要转换成上升沿触发的时钟。

DSP的CPU或DMA控制器与McBSP的通信,是通过16 bit的寄存器访问内部的外设总线来实现的。McBSP的数据接收寄存器2个,DRR1和DRR 2,当字长小于16 bit时使用DRR1。把McBSP要传输的串行字定义成为16 bit(刚好是10 bit A/D转换数据出的6个0+10 bit二进制数),并自行定义McBSP传输数据的一帧就是16 bit。这样McBSP接收完一帧数据后,就触发中断,进行这一帧数据的存储,然后进行下一帧数据的采样转换与传输,直到数据传输采集完毕。

下面是MeBSP配置成接收器要做的操作。

1)全局设置包括设置接收器的引脚为McBSP的引脚、使能或者禁止数字回环模式、使能或者禁止时钟停止模式、使能或者禁止多通道选择模式。

2)设置数据 即选择每个接收帧是单段还是双段、设置接收字长、设置帧长度、使用或者禁止忽略接收帧同步功能、设置接收压缩扩展模式、设置接收数据延迟、设置接收数据扩展和校验模式、设置接收中断模式。

3)帧同步设置 即设置接收帧同步模式、设置接收帧同步极性、设置采样率发生器帧同步周期和脉冲宽度。

4)时钟设置 即设置接收时钟模式、设置接收时钟极性、设置采样率发生器的时钟分频值、设置采样率发生器的时钟同步方式、设置采样率发生器的时钟模式(选择输入时钟)、设置采样率发生器输入时钟的极性。

调试程序所用的软件是TI公司的Code Composer Studio(CCStudio),它是TI公司开发的专用于进行TMS320系列DSP软件设计的集成软件开发环境。McBSP初始化程序如下:

3 结束语

本文以TMS320VC5502 DSP芯片与TLV1572模数转换芯片为例,详细讨论了TLV1572与DSP的多通道缓冲串口(MeBSP)通信的硬件接口和软件设计。其设计方案简单易行,具有一定的通用性,根据需要可以在中断服务子程序中嵌入适合的数据处理程序代码,就可以构成一个完整的数据采集与传输程序。本文中采集的数据是存放在TMS320VC5502芯片内部的RAM中,由于TMS320VC55x DSP的外部存储器接口(EMIF)支持8bi-t、16 bit、32 bit数据的访问,并为异步存储器、同步突发SRAM、同步DRAM提供了无缝接口,所以如果系统所要采集的数据量很大,也可以通过EMIF接口外扩存储器。

上一页 [1] [2] [3]