1、VDD电压产生电路

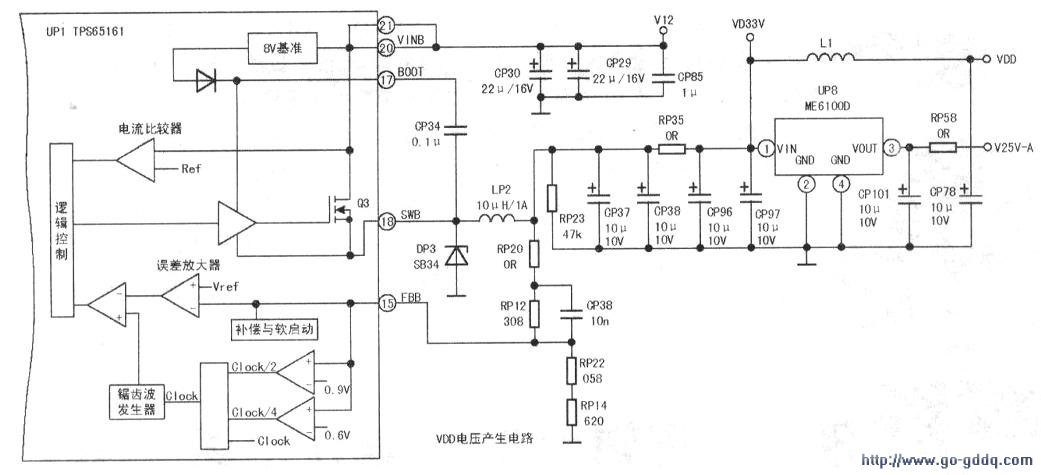

VDD电压产生电路由UPl(TPS65161)的(15)、(17)、(18)、(20)、(21)脚内部电路及UP8( ME6100D)等外围电路构成,其电路如下图所示。

上电后.TPS65161的⑩脚(ENl)接输入电压12V(高电平).(20)、(21)脚的输入电压分为两路:一路送到基准电压发生器,产生稳定8V电压,给驱动运放提供工作电压;另一路供给内部MOS开关管的漏极。时钟脉冲发生器产生的时钟脉冲送到锯齿波发生器中,经调制处理后输出调制脉冲到运放的同相输入端,误差放大器输出的控制电压输入到运放的反相输入端,经运放比较放大后,输出电压到驱动控制器中,产生驱动脉冲经驱动运放放大后驱动MOS开关管,从(18)脚输出开关脉冲,经DP3稳压,LP2、RP23、CP36、CP37、RP35滤波及限幅后得到VD33V电压。

该电压的一路经RP20、RP12与RP22、Rl,14分压后反馈到(15)脚,控制驱动脉冲的占空比,从而实现稳压控制。

第二路经Ll、CP78滤波,产生VDD电压,为驱动板上的时序控制器和扫描驱动器及数据器提供驱动电源;另一路经CP96、CP97 滤波后送到UP8( ME6100D)的(1)脚,经内部稳压后从(3)脚输出V25V -A电压,供驱动板上主芯片使用。

2.VAA_FB电压产生电路

VAA_FB电压产生电路由UPl(TPS65161)的(1)~(5)、(28)脚内部电路及外围电路构成,其电路如下图所示。UPl(TPS65161)(12)脚为主升压转换器工作方式设置,决定其内部电路是工作在脉冲宽度调制或500/750kHz固定开关频率方式。本方案中,(12)脚经RP25(oΩ电阻)接12V输入电压,工作在750kHz固定开关频率。

主升压转换器有一个可调节的软启动电路,以防止在启动过程中的高涌流。软启动时间由连接到(28)脚的外部电容器CP26设置。(28)脚内部连接一恒流源,与内部电流限制与软启动脚电压成正比。在达到内部软启动的阈值电压时,比较器被释放电流限制。软启动电容器值愈大,软开始时间越长。

上电后,12V输入电压经CP5、CP6、LP3滤波后,一路加到DP1、CP7、CP8、CP9、CP10组成的滤波电路,产生VAA_FB电压;另一路加到UPl(TPS65161)的(4)、(5)脚。

VAA_FB电压经CP16滤波后加到UPl(TPS65161)的(3)脚,(3)脚内接一个过电压保护开关Q2和过电压保护比较器,过电压保护比较器将(3)脚电压与内部基准电压进行比较,当(3)脚电压上升到23V时,TPS65161内部驱动控制器关掉N通道MOSFET,只有输出电压低于过电压阈值后,内部驱动控制器才会再开始工作。