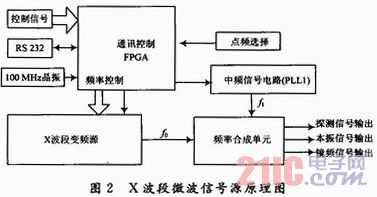

2.1 通信控制单元

通信控制单元采用现场可编程门阵列(FPGA)编程实现。FPGA具有集成度高,数据处理速度快,系统结构设计灵活等特点,可以根据需要通过布局布线工具对其内部进行编程,将电路集成在一个芯片上,在最短的时间内设计出专用系统。

FPGA通过RS 232与上位机通信,通信接口采用MAX 232实现电平转换,在数据接收端将±10 V电平信号转换为FPGA兼容的TTL电平,在数据发送端将TTL电平转换为±10 V电平信号,满足标准RS 232接口的电平要求。

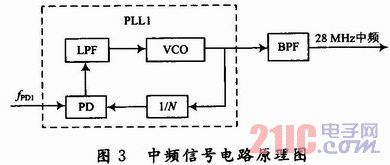

2.2 中频信号电路

中频信号电路采用数字锁相环实现,100 MHz晶振经过FPGA分频电路生成4 MHz的基准频率作为PLL1的参考频率FPD1,锁相环PLL1的分频比N=7,输出信号滤波后产生项目要求的28 MHz中频。中频信号电路原理如图3所示。

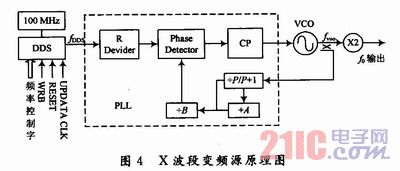

2.3 X波段变频源

X波段变频源采用DDS驱动PLL结构的宽带频率源设计,电路原理如图4所示。

DDS选用AD9854芯片,内置48位相位累加器,并且具有两个内部的高速高性能D/A转换器,通过对外部参考时钟倍频,其内部时钟可达到300 MHz,可以很方便地产生低频的参考信号,并且具有较好的动态性能。

DDS的各种读/写及控制信号由FPGA提供,为了使DDS和FPGA之间的系统时钟同步,它们的外部参考时钟fref由同一个100 MHz的温补晶振提供。DDS输出的信号频率fDDS由FPGA写入的频率控制字控制,锁相环PLL的参考信号由DDS的输出信号驱动,VCO的输出频率由PLL芯片的电荷泵CP输出端控制,通过对VCO输出的信号进行倍频得到X波段f0输出信号。

PLL模块选用ADF4106宽带数字锁相环芯片,ADF4106由低噪声鉴频鉴相器、高精度电荷泵、可编程参考时钟分频器、可编程双模预分频器构成,其带宽可以达到6 GHz,具有较短的频率建立时间和较低的相位噪声,选择低相位噪声的数字锁相环有助于保证整机的低相噪性能。

采用的PLL芯片具有一个双模预置分频器,可产生大分频比,这就使频率综合器在输出较高频率信号的同时仍保持较高的频率分辨率。

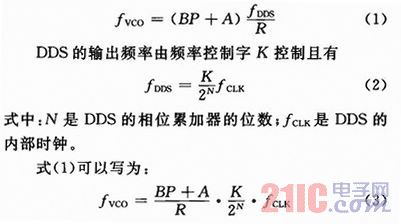

VCO输出信号的频率和DDS输出信号的频率间的关系为:

从式(3)可以看出,采用DDS模块后的输出信号具有比传统结构更高的频率分辨率。

环路滤波器选用AD820运算放大器进行环路滤波器的设计与实现,使用ADISimPLL软件计算环路滤波器各元器件的参数。