前言

随着多媒体通信技术的发展,人们不再满足单一文字或声音的传递,从普通电话到视频电话,从SMS(short messaging servICe)到EMS(enhanced message service)再到MMS(multimedia messaging service),多媒体技术逐渐进入千家万户。因此,研究如何高效地处理多媒体信源,让其更方便有效地存储和传输是非常必要的。JPEG标准作为图像压缩编码的一项重要技术,不仅适用于静止图像的编码,其分支M-JPEG也适用于低成本场合的运动图像编码。现在的图像显示卡已发展到高速处理3D图像的水平,但是,对静止图像JPEG压缩的评测仍是一项基本指标。

目前的嵌入式处理器种类繁多。ALTEra公司的Nios II处理器是用于可编程逻辑器件的可配置的软核处理器,与Ahera的低成本的Cyclone FPGA组合,具有很高的性价比。本系统采用Nios II和CycloneEP1C6嵌入式系统开发板,以及VGA显示器,实现了一个嵌入式JPEG图像显示系统。

1 总体设计及系统架构

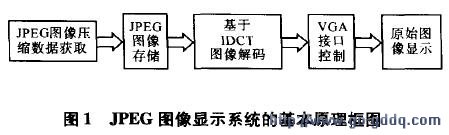

JPEG图像显示系统有三大功能:JPEG图像的存储、解码和显示。基本原理如图1所示。利用串口通信、USB接口或以太网数据传输获取JPEG图像压缩数据并将数据存入高速存储器(Flash或SRAM);图像的解码主要包括预处理、HufFMan解码、反量化、IDCT变换;图像显示是将解码后的图像数据转换为适合VGA工业标准的RGB信号,再利用D/A转换,最后显示原始图像。

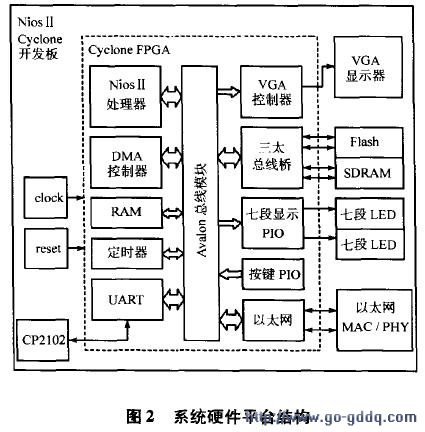

该系统在结构上分为3层:系统硬件平台、操作系统和基于IDCT解码算法。最底层是系统硬件平台,是系统的物理基础,提供软件的运行平台和通信接口。系统的硬件平台在Altera的Nios II Cyclone嵌入式系统开发板上实现,显示器采用VGA标准的显示器,可输出大小为640×480像素、分辨率为500 dpi的24位真彩色图像。第2层是操作系统,采用uCOS II。uCOS II是一个基于抢占式的实时多任务内核,可固化、可剪裁、具有高稳定性和可靠性。这一层提供任务调度以及接口驱动,同时,通过硬件中断来实现系统对外界的通信请求的实时响应,如对以太网数据流传输的控制、对串口通信的控制等。这种方式可以提高系统的运行效率。最上层是JPEG图像解码核心算法的实现。该算法高效地对压缩图像数据进行解码处理和空间域的转换。采用C语言在Nios II的集成开发环境(IDE)中实现。

2 系统硬件的设计与实现

2.1 NiosⅡ 嵌入式软核处理器简介

Nios II嵌入式处理器是Altera公司于2004年6月推出的第2代用于可编程逻辑器件的可配置的软核处理器,性能超过200 DMIPS。基于哈佛结构的RISC通用嵌入式处理器软核,Nios II能与用户逻辑相结合,编程至Altera的FPGA中。处理器具有32位指令集,32位数据通道和可配置的指令以及数据缓冲。它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统(SoPC)设计了一套综合解决方案。Nios II处理器系列包括3种内核:一种是高性能的内核(Nios II/f);一种是低成本内核(Nios II/e);一种是性能/成本折中的标准内核(Nios II/s),是前两种的平衡。本系统采用标准内核。

Nios II处理器支持256个具有固定或可变时钟周期操作的定制指令;允许Nios II设计人员利用扩展CPU指令集,通过提升那些对时间敏感的应用软件的运行速度,来提高系统性能。

2.2 硬件平台结构

系统的硬件平台结构如图2所示。本系统采用USB至UART桥接器CP2102实现与上机位的通信。由SILicon Laboratories推出的CP2102,使RS232升级到USB接口更加简单,原先采用RS232串口通信方案的设备在软件上无需作改动即可直接升级到USB。CP2102内建EEPR0M、稳压器、USB收发器和整合式内部振荡器。这套组件还包含完整的USB2.0全速(ful1.speed)装置控制器、桥接控制逻辑以及传送/接受缓冲器和调制解调器商议讯号(handshake signa1),这些功能全都整合至5 mm×5 mm的小型封装内。图像数据传输的流程是:首先初始化串口UART的各个寄存器,主要是接受寄存器(rxdata)、发送寄存器(tx.data)、状态寄存器(status)、控制寄存器(contro1)、波特率分频器(divisor)等;然后传输等待,图像数据以1 15 200 bps的速率进人数据寄存器,再通过DMA存入Flash。

本系统硬件平台主要是在Nios II Cyclone嵌入式开发板上实现。系统的主要组件,包括Nios II的标准内核、片内存储器、UART、DMA控制器、并行I/O接口、Avalon总线、定时器等都集成在一块Ahera的cyclone FPGA芯片上,使用SoPC Builder来配置生成片上系统。

SoPC Builder是功能强大的基于图形界面的片上系统定义和定制工具。SoPC Builder库中包括处理器和大量的IP核及外设。根据应用的需要,系统选用Nios II Processor、On Chip Memo~、Flash Memo~(Common Flash Interface)、SDRAM Controller、UART、DMA、Interval timer、Seven Segment PIO、Avalon Tri StateBridge、Ethernet Interface等模块。对这些模块配置完成后,使用SoPC Builder进行系统生成。SOPC Builder自动产生每个模块的HDL文件,同时自动产生一些必要的仲裁逻辑来协调系统中各部件的工作。

(