・上一文章:基于加速度的车祸报警系统的设计与实现

・下一文章:基于DDS的寄生电感测量仪设计

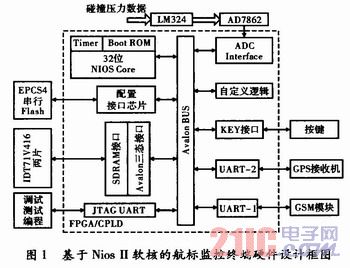

摘要 阐述了基于NiosⅡ软核的内河航标监控系统的设计方法,及AD7862控制电路的VHDL设计。从系统的角度提出航标监控系统的完整设计方案,给出基于Nios II的航标监控终端硬件设计框图,并得到在Modesim中进行仿真的结果。根据现场运行情况显示,系统能实时地监测航标的工作状态,达到系统工业级的品质保证,并且具有高可靠性、高实时性和维护方便性等优点。

关键词 Nios II;SOPC builder;FPGA;航标监控系统

内河水运是国家综合运输体系和水资源综合利用的重要组成部分,是实现经济社会可持续发展的重要战略资源。航标是内河航道的基础助航设施,传统的航标管理模式落后,标准化程度低,实时性、安全性能差,已无法满足当前日益繁忙的航道运输所提出的高质量安全航行的需求。

Nios II是ALTEra公司推出的基于RISC技术的软核CPU,作为一种用户可随意配置和构建的32位总线嵌入式系统微处理器软核,它的硬件设计方面用户是可自定制的,具有灵活性和可裁减性等优点。

结合内河航道航标管理的实际情况,介绍了一种新的基于Nios II软核的航标监控系统的设计方案。根据系统的运行结果显示,设计实现了系统预期功能,为监控中心能实时地监测航标的工作参数与状态,管理信息,及时发现故障,从而提高航标的可靠性,增强航道航行的安全性,提高管理效率。

1 系统终端硬件电路的实现

航标监控系统终端硬件设计主要包括GSM短消息发送模块、GPS数据采集模块、碰撞压力处理电路等组成的外围设备,还有以32位Nios II CORE为主体的核心逻辑两个主要部分组成,系统终端硬件框图如图1所示。