系统硬件设计

系统的硬件系统包括FPGA、存储器和外围元器件3个部分。FPGA部分需要在SOPC Buider中设计,包含NiosII CPU核、内部时钟、Avalon总线控制器、连接NiosII核的下载和调试程序的JTAG_UART通信模块、DDS接口模块及DDS模块、FIR、IIR数字滤波器接口模块及功能模块、编/解码模块及接口模块、Flash存储器模块等。各外设模块核通过在片上的Avalon总线与NiosII相连。为使具有DSP处理器功能的NiosII系统正常工作,在FPGA外围接有一些控制键,以调度各模块的应用。

建立Nios II嵌入式处理器系统

首先利用QuartusII建立项目工程,选用的目标器件为CycloneEPIC12,用SOPC Buider创建NiosII组件模型,生成硬件描述文件,锁定引脚后进行综合与适配,生成NiosII硬件系统下载文件。然后建立NiosII嵌入式系统,从SOPCBuider组件栏中加入需要的各种组件:如NiosIICPU Core、定时器Timer、JTAG_UART、Avalon三态总线桥、键输入I/O口、Flash等。另外,为了实现NiosII处理器对EPCSFlash存储器的读写访问,还要加入一个EPCS Serial Flash Controller组件,通过此控制器将用于FPGA配置的SOF文件和CPU运行的软件一并存于EPCS器件中,以便大大简化硬件系统组成结构。为了保证所有组件的地址安排合法,要对各组件地址进行自动分配,最后进行全程编译,即进行分析、综合、适配和输出文件装配,以完成NiosII硬件系统的设计。 在NiosII硬件系统设计完成后,将配置文件下载到指定的FPGA中。通过SOPC Buider软件窗口,可进入NiosII DSK软件开发环境进行软件设计。

DSP处理器功能系统的建立

使用DSP Buider在FPGA上进行DSP模块的设计,可实现高速DSP处理。但是,在实际应用中,由于DSP处理的算法往往比较复杂,如果单纯使用DSP Buider来实现纯硬件的DSP模块,会耗费过多的硬件资源,有时也无法完成复杂的运算。在DSP算法巾反复出现的一些运算,如复数乘法、整数乘法、浮点乘法等,在通用的CPU中都没有专门的相关指令。利用Nios II的自定制指令特性,在系统设计中,可利用MATLAB、DSPBuider或VHDL设计并生成复数乘法器、整数乘法器、浮点乘法器等硬件模块,在QuartusII环境中对上述文件作一些修正后,在SOPC Buider窗口中将它们定制为相应的指令,并可设定或修改执行该指令的时钟周期。在进行DSP算法运算时,可通过汇编或C,甚至C++来运用这些自定义指令进行嵌人式程序设计。

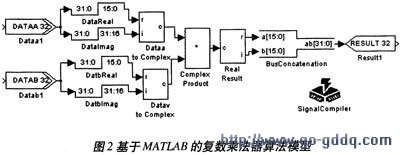

用MATLAB、DSP Buider设计的复数乘法器模型如图2所示,它完成了16位的复数乘法,虚部和实部的位宽都是16位,可以用一个32位的值来表示该复数。在设计中,NiosII为32位数据,正好可以放置2个复数。

要将这个复数乘法器硬件模块设置成相应的指令,还要进行以下操作:单击图标SignalCompiler对其进行转换,选择器件(用Cyclone)、选择Quartusll综合器,转换后使其生成SOPCBuider的PTF文件。退出MATLAB后,在QuartusII环境中对转换后所生成的复数乘法器的顶层VHDL文件进行修改。在SOPCBuider窗口中双击cpu项,进入指令加入编辑窗;单击Import按钮,进入加入模块文件窗口;单击Add按钮,打开顶层文件;单击Read port-list from files按钮,得到端几加人情况显示窗口;单击Add to System按钮,加入复数乘法器设计模块,将这个硬件模块设置成白定义的复数乘法指令comp。还可以修改该指令的指令周期。单击Generate按钮,进行SOPC生成。

另外,NiosII的外设是可任意定制的,NiosII系统的所有外设都通过Avalon总线与NiosII CPU相接。Avalon总线是一种协议较为简单的片内总线,NiosII通过Avalon总线与外界进行数据交换。在本系统中,采用Avalon Slave外设方式加入了自定制Avalon总线组件A/D转换接口模块、D/A接口模块,用于控制采样ADC的工作并控制高速DAC的波形数据输出。而白定义的Avalon总线组件DDS模块接口和DSP功能转换控制接口则用于NiosII CPU对DDS模块的控制及通过外部键盘来控制DSP功能的选择。

系统软件设计

指令生成并加入总线和各种需要加入的外设组件(如各类接口、flash等)后,对基于NiosII的SOPC系统进行编译并下载到FPGA中。在NiosII的硬件系统生成的同时,SOPC Buider帮助用户生成相应的SDK(软件开发包)。由于在硬件开发中的Nios CPU及其外设构成的系统是自定制的,存储器、外设地址的映射等都各不相同,需要专有的SDK,用户新定制的指令也必须修改原有的编译工具,这些都由SOPC Buider自动生成。

在生成SDK的基础上,可进入系统软件的设计。在这里,软件的开发设汁与通常的嵌入式系统的开发设计相类似,唯一不同点在于这时面对的嵌入式系统是自己定制的、裁剪过的,因此,受到硬件的局限性会小些。可使用汇编、C、C++来进行嵌入式程序设计,使用GNU工具或其它第三方工具进行程序的编译连接以及调试。

比如,将复数乘法器硬件模块设置成相应的指令后,锁定引脚,全程编译。然后利用QuartusII编辑C程序进行测试。在FPGA中的NiosCPU中运行C程序。测试成功后,在DSP计算中遇到复数乘法就可以运用复数乘法指令。

DDS模块还是以硬件形式固化在FPGA中,可以根据需要,利用DDS设计出幅度、相位和频率调制器。

结语

这种将常用的硬件模块生成指令,软、硬件并存的设计方法在FPGA中可实现较复杂的DSP运算。整个系统除了ADC、DAC和控制选择键盘外,都可在1片FPGA可编程芯片中实现。还可通过Avalon总线白定义各种接口模块组件,提高整个DSP系统的灵活性,将软件的灵活性和硬件的高速性予以结合。