・上一文章:基于S3C2440的车载GPS/GPRS跟踪监控系统研究与实现

・下一文章:大气机高度输出接口电路的设计

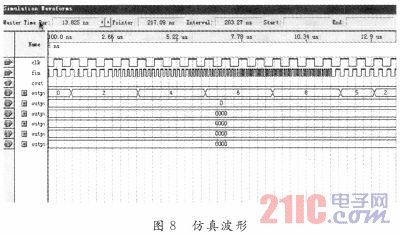

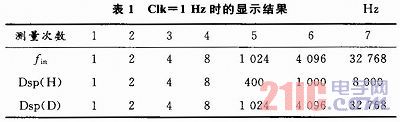

在GW48系列SoPC/EDA实验箱上下载、调试后,被测信号为fin为十进制,实验箱上的显示值为DSP(H)。Dsp(H)为十六进制,Dsp(D)为十进制,Clk=1 Hz,通过从实验箱上给出的频率值来验证,从表1可以看到显示结果。

从表1可以看出所显示的结果与被测信号的频率一致。从信号发生器中输入测频范围内的任意频率也可验证。

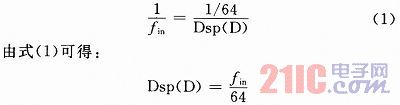

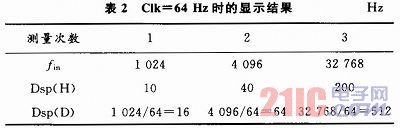

还可以改变控制信号即Clk的大小从而改变测量范围,当Clk=64 Hz时,理论值为:

把实验箱上给出的频率值做被测频率,从表2可以看到显示结果。

从表2可以看出所显示的结果转换后与被测信号的频率一致。

4 结语

采用此种方法设计的简易数字频率计简单、直观,测频范围随时可根据用户需要进行调整,占用的CPLD芯片资源较少,不失为一个很好的数字频率计设计解决方案。由此可见,采用这种技术设计的数字电子系统,大大减少了电路板的尺寸,同时增加了系统可靠性和设计灵活性。