摘要 设计了一种应用于流水线ADC中的新型高线性度采样开关,该开关采用比较器、反相器链、CMOS对管开关,自举电容等实现,具有较高的线性度。其基本原理为:使MOS管栅极电压实时跟随输入电压,保证其差值恒定,从而实现整体采样保持电路较高的无杂散动态范围。通过flip-around型采样保持电路进行验证,其无杂散动态范围可达91dB,满足设计要求。

关键词 采样开关;栅源跟随;高线性度

在ADC转换器的设计和应用中尤其在音频、视频系统中,谐波失真是要考虑的因素,对于传统ADC的采样开关而言,CMOS对管,用MOS管作为开关使用时是不分漏源级的,当实际采样到的信号不断变化时,其源级也无法确定,这就导致无法通过将源级和衬底相连的方式消除衬底偏置效应,从而导致开关的非线性较大,这对ADC的非线性影响也较大。

针对此问题,基于MOS管栅源级电压跟随技术,设计了一种新型高精度采样开关,能有效减小MOS管的衬底偏置效应,可广泛应用于流水线ADC,逐次逼近ADC等模数转换器和各种采样系统中,具备良好的线性度。

1 采样开关的设计

1.1 工作原理

本项目设计14位100 MHz采样速率的高精度采样保持电路,考虑到实际电路中的寄生非理想特性,ADc中采样保持电路的谐波失真主要由采样开关的导通等效电阻,沟道电荷注入效应以及输入寄生电容等因素影响。为确保一定的线性度和输入信号带宽,文中对传统CMOS对管开关电路进行了优化和重新设计,确保满足系统高线性度的要求。

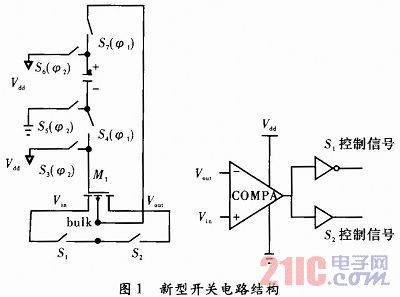

如图1所示,设计的新型开关主要由基本CMOS对管开关,比较器和反相器链组成。由于要实时判断哪个端口为源级和漏级,因此加入了2个衬底选择开关S1和S2,由互补开关组成。采用比较器触发S1和S2使衬底能够连接到实时变化的源端。在采样开关M1管导通的状态,衬底确保能够只连接到一个端口。采用直接连接源端和衬底的结构,使M1管的偏衬效应得以消除,使其具有较小的非线性和较大的输入摆幅。下面讨论两种情况,分别分析M1管分别导通和关断时的工作原理。

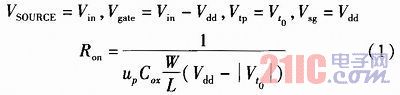

在关断时(S6,S5和S3打开),自举电容会被充电到Vdd。在导通时(S7和S4打开),当Vin<Vout,即比较器输出为低电平时S1打开,直接连接输入端和衬底。采样开关M1的栅极电压此时等于Vin-Vdd,源栅电压Vsg和源衬电压Vsb分别接到电源电压Vdd和0。根据MOS管基本公式可得

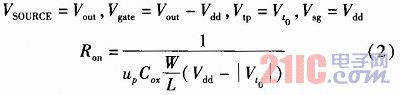

当Vin>Vout时,情况和前面正相反。开关S2由比较器作用以连接输出端和衬底,对应此时真正的源端是输入端。采样开关M1的栅极电压变成Vout-Vdd,同时源端电压是Vout。此时Vsg仍然准确地为Vdd不变,阈值电压同样不变。与式(1)类似,同理可得