3 DSP系统实现

DSP实现啸叫抑制阶段主要包含语音信号的采集、啸叫通道的建立、信号移频处理、语音信号的输出等部分。

3.1系统硬件结构

6713是TI公司6000系列的一款非常经典的新型浮点DSP芯片。它最高主频可达300 MHz,处理速度高达2 400 MPIS;片上外设资源也很丰富,本系统将用到其两个多通道缓冲串口(McBSP) 0 6713的优异的性能使之特别适合于高精度应用,如在专业音频、数据采集、去噪、医疗和诊断图像应用等领域。

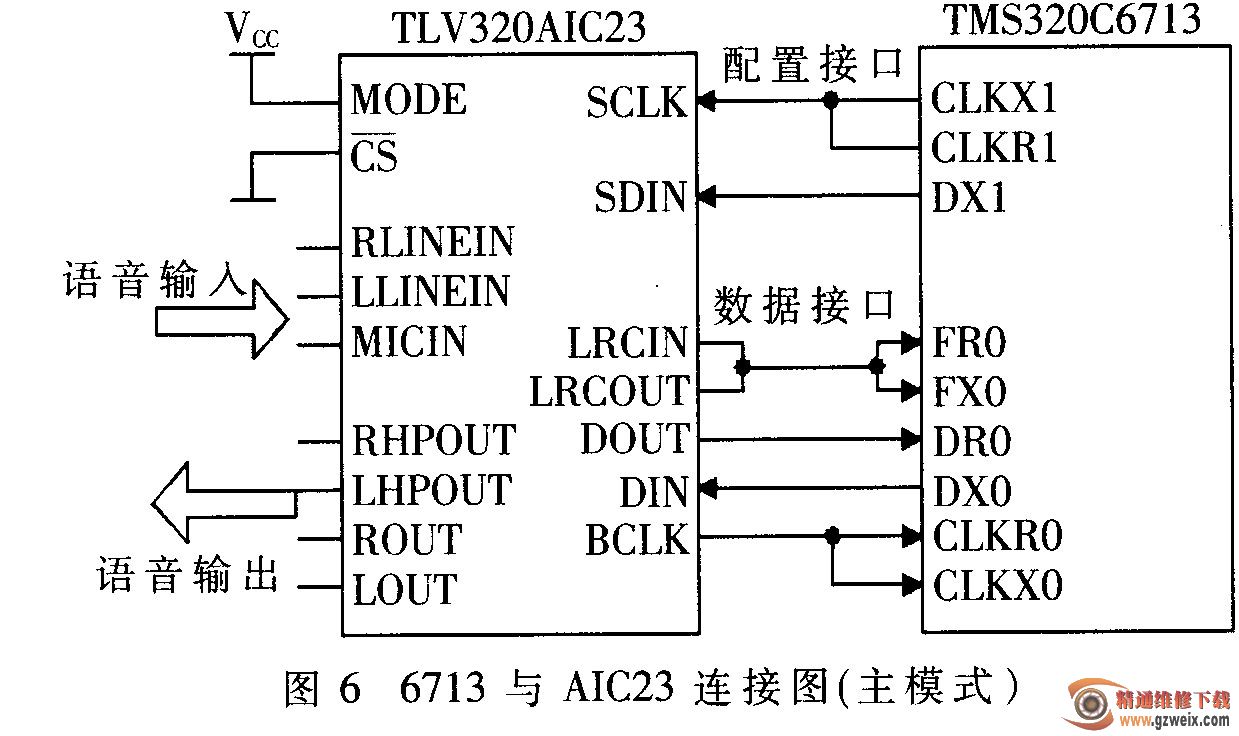

图6为6713与Codec芯片TLV320AIC23(以下简称AIC23)的连接示意图,即语音的采集(A/D转换)和回放 (D/A转换)环节。AIC23是TI公司生产的一款高性能立体声音频编解码器,含有模拟/数字音频接口、控制接口、时钟管理、电源管理等部分。AIC23内部集成的模/数转换和数/模转换部件采用了先进的Sigma-Delta过采样技术,可以在8 kHz - 96 kHz的频率范围内提供16 bit,20 bit、 24 bit和32 bit的采样。

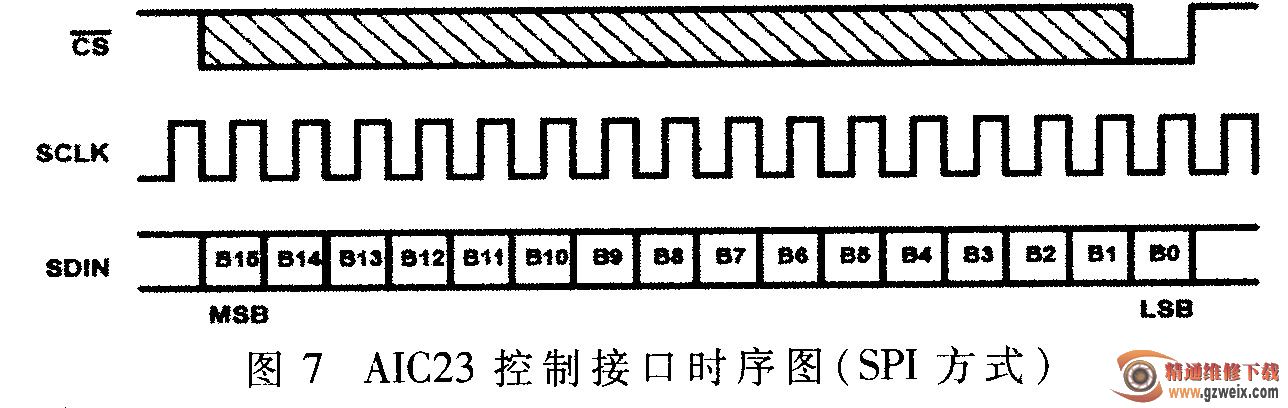

在Codec的控制环节中,根据MODE引脚电平可决定它是工作在12C (2线)模式还是SPI (3线)模式,图6中此引脚接高电平,即工作在SPI模式下,此时与之连接的McBSPI也必须配置为SPI这种全双工通信的模式(此时CLKX和CLKR内部相连),这也正体现了AIC23与McBSP之间能进行无缝连接。此外,因为Codec的控制接口只是用来接收DSP发出的配置寄存器的命令(即单向,只接收数据通道),所以此SPI模式中没有串行输出数据线,即“三线”模式而非SPI传统的四线模式。CS是帧同步信号,SCLK与SDIN分别是串行数据时钟、串行输人数据线。DSP发出的控制命令是16 bit的且总是从MSB(最高位)开始。图7所示的时序图中bit为11个AIC23寄存器的7位地址,后9位是欲配置的值,所以此处编程须注意将数据移1位。本系统将Codec配置为16 kHz采样、16 bit量化、双声道、MIC采集模拟语音信号输人、HeadPhone输出模拟语音信号。

数据通道环节中,图6中Codec芯片通过DSP的McBSPI口进行语音数据的A/D和D/A转换(即全双工的数据通道)。芯片数字音频接口部分有bit时钟信号BCLK、数据输人/输出DIN和DOUT、帧信号LRCIN和LRCOUT。 AIC23支持多种音频接口模式,这里将其配置为主模式和与TI DSP的McBSP相兼容的DSP模式。这样,BCLK就会输出时钟信号,而LRCIN和LRCOUT就必须连接到DSP的帧同步信号FS引脚上。如图8所示,采集到的数据也是从MSB开始传输,这里将AIC23的Digital Audio Interface Format寄存器配置为先发送16 bit的左通道数据,紧接着发送16 bit的右通道数据。