・上一文章:基于DDS芯片的相位相关双通道信号源设计

・下一文章:基于安培力的金属与非金属自动分离垃圾箱

2 RTL级建模与联合仿真验证

2.1电路的RTL级模型

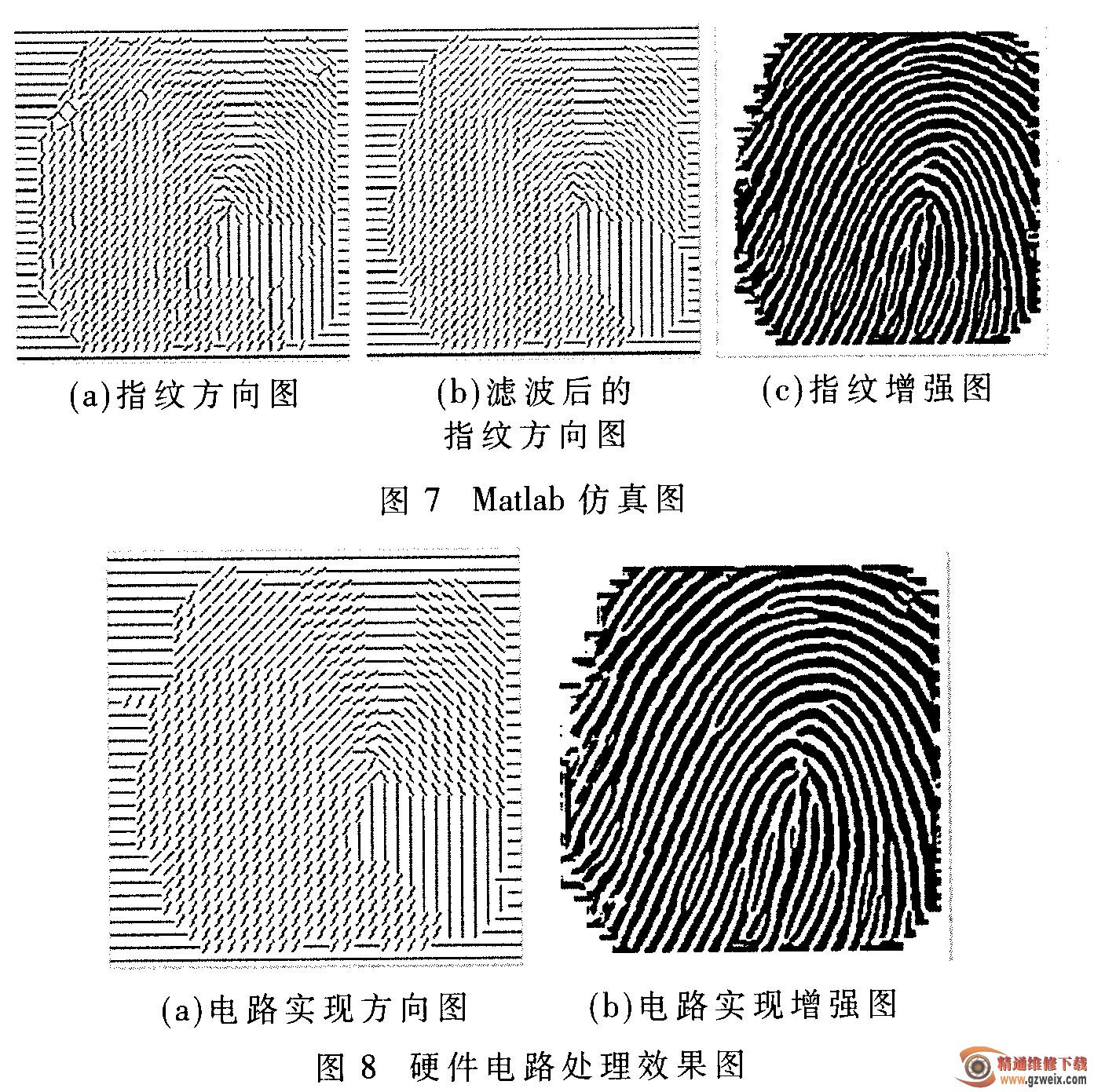

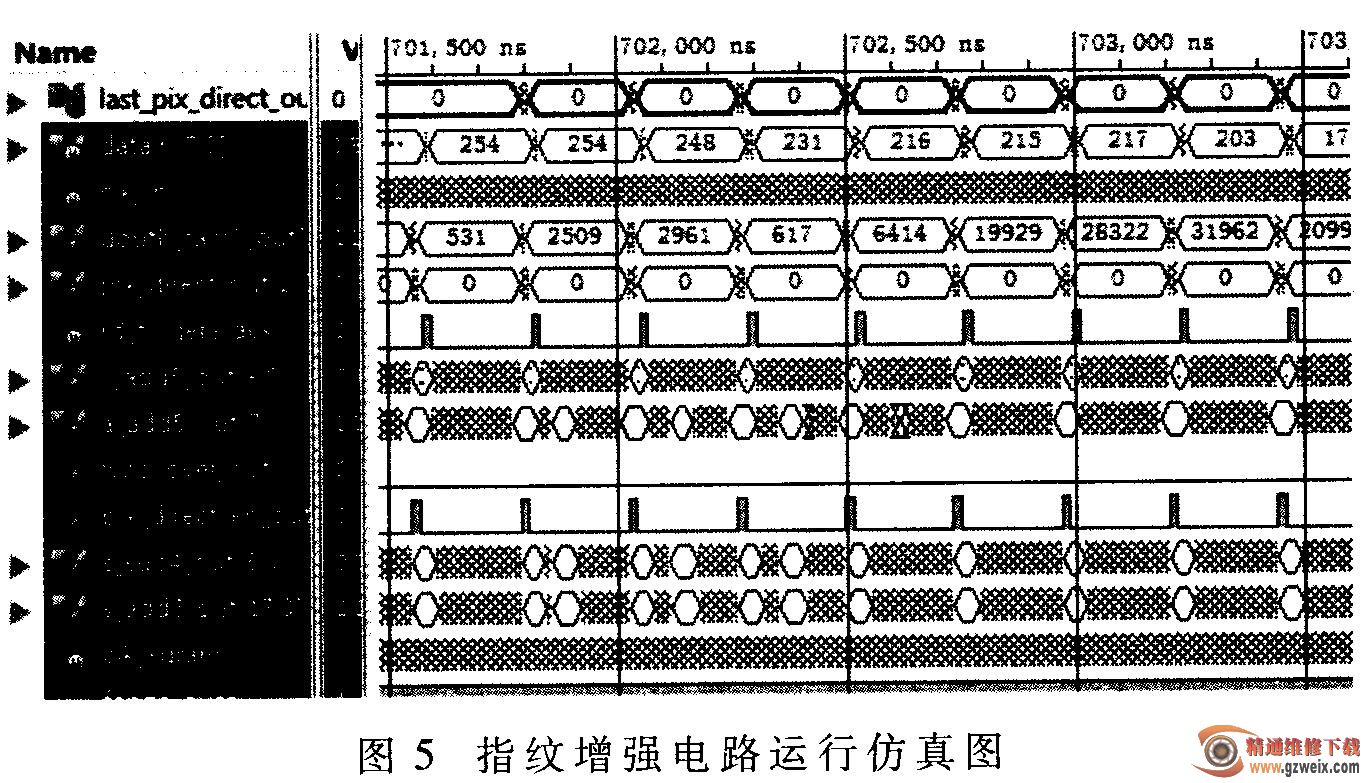

电路的设计基于硬件描述语言Verilog编写完成。采用自下而上的设计方法,先规划整个电路结构,将整个电路划分为点方向计算模块、块方向计算与滤波模块、指纹图增强模块三个部分;然后设计每一个基本模块,往上设计总体模块,顶层采用原理图方式。整体芯片仿真部分信号时序如图5所示。

2.2联合仿真验证

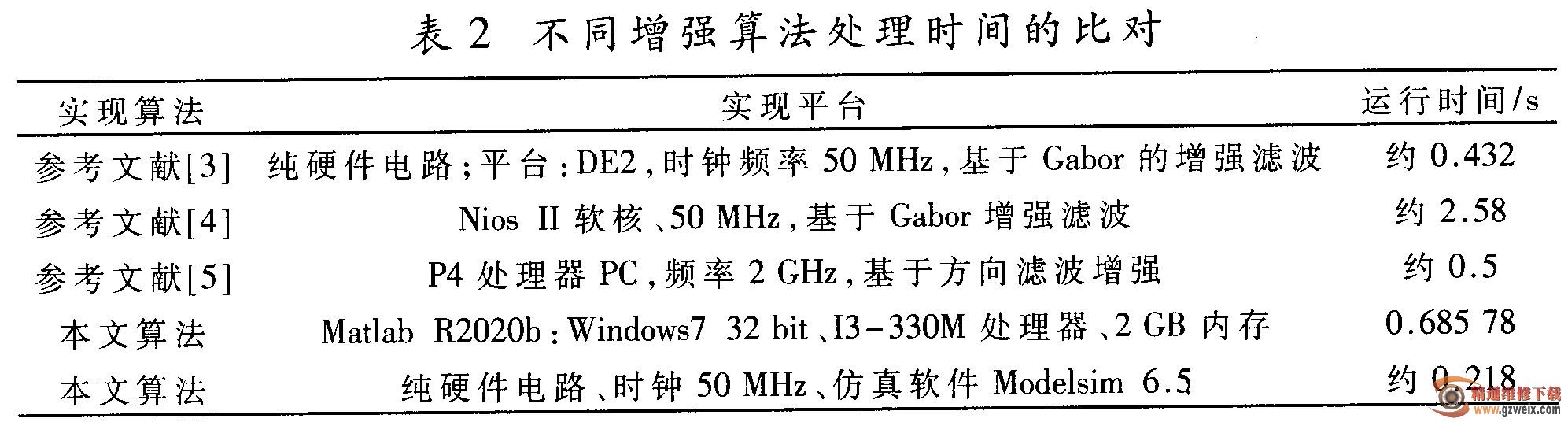

编写Verilog仿真模型,在Modelsim中进行功能测试仿真,将电路计算的输出数据均用文本输出保存,然后联合Matlab工具,将最终电路处理输出的结果通过Matlab直观地显示出来以供分析。图6为指纹原图,图7、图8所示为实际仿真测试图,表2为本文算法处理时间与其他算法处理时间的比较。