结果得到了一个与晶体管尺寸有关的电流表达式,由式中可以看出,输出功率管M21的静态电流由M13,M21,M23,M24的宽长比与电流决定,与输入信号无关。因此,预先设定好四个管子的宽长比,给M13,M23,M24以固定的电流,输出功率管的静态电流就被确定下来了。但是运放中加入四个MOS管是否不会影响运放的其他性能。从信号通路的角度看,晶体管M11,M12,M13,M14中只流过直流电流,没有交流电流从中通过,它们屏蔽了交流行为,对来自第一级的电流表现为一个无穷大的交流阻抗。这四个MOS管设置了输出功率管的静态电流,但是对于第一级的增益、带宽均不起作用。所以放大器的增益仍然为:

使用跨导线性环的目的是当一个输出晶体管流过大电流时,防止另一个输出晶体管关断。实际上,当M21流过一个大的输出电流时,M22就有可能被关断。在流过大的输出电流的情况下,至少要保证M22上能流过一个最小的电流,这样就可以减少交越失真并且提高速度。

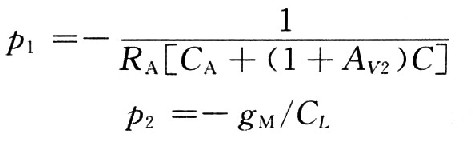

对于这样的多极点两级运放来说,在输出端电阻和电容串联做米勒补偿,以增大相位裕度,提高稳定性。通过频率补偿,两个主极点分别为:

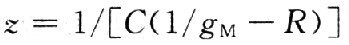

式中:RA是从M9漏端到地的总阻抗;CA是M9漏端到地的总寄生电容;CL是输出端的总电容。p1是第一级放大器的输出端产生的极点,米勒补偿后离原点最近,成为主极点;p2是输出端产生的极点。米勒补偿后离原点较远。同时由于电阻和电容形成了通路,产生一个零点:

适当调节R,使z=p2,可使零点与第二主极点相互抵消,增加了系统的稳定性。

2 仿真结果及分析

仿真性能参数如表1所示。用Cadence Spectre进行仿真。使用了华润尚华0.5μm的N阱CMOS工艺模型,模拟环境是VDD=5 V,T=27 ℃典型条件。在5 V单电源下驱动8 Ω负载。对于1 kHz,4 V峰一峰值的正弦波激励,仿真得到负载上的电压基波幅度为3.9l V。此时电源消耗的平均功率为3.15 W,功率放大器的效率为60.7%。总谐波失真为0.098%。总体上THD和效率随输入电压变大而增加。放大器频域响应如图3所示。

3 结语

该设计的AB类输出功率放大器电路,采用折叠式共源共栅结构,功率管推挽式输出,同时利用外部电流源供电,采用低压共源共栅电流镜结构的偏置电路。仿真结构表明该运放具有高增益,低输入失调电压,低THD等特点,同时具有良好的频率特性,较低的静态功耗,满足一块高性能的AB类音频功放芯片的要求。

上一页 [1] [2]