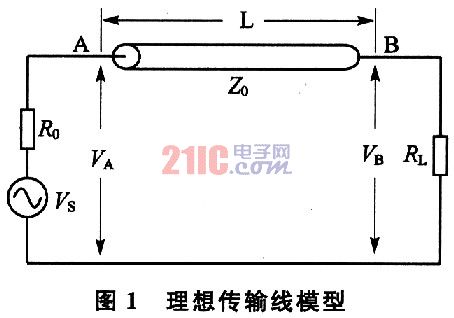

用图1所示的理想传输线模型来分析与信号反射有关的重要参数。图中,理想传输线L被内阻为R0的数字信号驱动源VS驱动,传输线的特性阻抗为Z0,负载阻抗为RL。

负载端阻抗与传输线阻抗不匹配会在负载端(B点)反射一部分信号回源端(A点),反射电压信号的幅值由负载反射系数ρL决定:

式中ρL称为负载电压反射系数,它实际上是反射电压与入射电压之比。

由式(1)可见,-1≤ρL≤+l,且当RL=Z0时,ρ1=O,这时就不会发生反射。即只要根据传输线的特性阻抗进行终端匹配,就能消除反射。从原理上说,反射波的幅度可以大到入射电压的幅度,极性可正可负。当RL<Z0时,ρL<O,处于过阻尼状态,反射波极性为负;当RL>Z0时,ρL>O,处于欠阻尼状态,反射波极性为正。

当从负载端反射回的电压到达源端时,又将再次反射回负载端,形成二次反射波,此时反射电压的幅值由源反射系数ρS决定:

传输线的端接通常采用两种策略:负载端并行端接匹配、源端串行端接匹配。只要负载反射系数或源反射系数二者任一为零,反射都将被消除。并行端接在信号能量反射回源端之前在负载端消除反射,即使ρ1=O,消除一次反射,这样可以减小噪声、电磁干扰(EMI)及射频干扰(RFI);串行端接则是在源端消除由负载端反射回来的信号,即使ρS=O和ρL=1(负载端不加任何匹配),只是消除二次反射,在发生电平转移时,源端信号会出现持续时间为2TD(TD为信号源端到终端的传输延迟)的半波波形,这意味着沿传输线不能加入其他信号输入端,因为在上述2TD时间内会出现不正确的逻辑态。两种端接策略各有其优缺点,不过由于并行端接的匹配网络需要与电源连接,使用较为复杂;串行端接只需要在信号源端串入一个电阻,消耗功率小而且易于实现,有较大的实际工程应用价值,所以被广泛采用。

2.2 防止地弹

当PCB板上的众多数字信号同步进行切换时(如CPU的数据总线、地址总线等),由于电源线和地线上存在阻抗,会产生同步切换噪声(Sim-tl ltaneous Switch Noise,SSN)。与此同时,由于芯片封装电感的存在,在电路同步切换过程中形成的大电流涌动会引起地平面的反弹噪声(简称为地弹),这样在真正的地平面(0 V)上就要产生电压的波动和变化,这个噪声会影响其他元器件的动作。

SSN和地弹的强度也取决于集成电路的I/O特性、PCB板电源层和地平面层的阻抗以及高速器件在PCB板上的布局和布线方式,负载电容的增大、负载电阻的减小、地电感的增大、同时开关器件数目的增加均会导致地弹的增大。在高速PCB电路设计中可以采取以下一些基本措施来减小SSN和地弹的影响:

①降低输出翻转速度。一些新的总线驱动器件采用内嵌的电路设计,在对传输延时影响最小的前提下,降低翻转速度。

②采用分离的专门参考地。分离的参考地由于电流很小,地反射现象会大大减小。分离地的芯片要注意使每个地线能够有直接到地平面的最短路径。

③降低系统供给电源的电感。高速电路设计中要求使用单独的电源层,并让电源层和地平面尽量接近。

④降低芯片封装中的电源和地引脚的电感。比如增加电源/地的引脚数目,减短引线长度,尽可能采用大面积铺铜。

⑤增加电源和地的互感。要让电源和地的引脚成对分布,并尽量靠近。

⑥给系统电源增加旁路电容,这些电容可以给高频的瞬变交流信号提供低电感的旁路,而变化较慢的信号仍然走系统电源回路。

2.3 减小串扰

PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

串扰电压的大小与两线的间距成反比,与两线的平行长度成正比,但不存在倍数关系。在实际高速电路中进行布线时,当布线空间较小或布线密度较大时,应慎重对待信号线之间的串扰问题,高频信号线对与其相邻的信号线的串扰可能会导致门级的误触发,这样的问题在电路调试的过程中是很难被发现并妥善解决的。

随着干扰源信号频率的增加,被干扰对象上的串扰幅值也随之增加;信号的上升/下降时间或边沿变化(上升沿和下降沿)对串扰的影响更大,边沿变化越快,串扰越大。

由于在现代高速数字电路的设计中,具有快速上升时间的器件的应用越来越广泛,因此对于这类器件,即使其信号频率不高,在布线时也应认真对待,以防止产生过大的串扰。

传输线与地平面的距离(即传输线与地平面之间的电介质层的厚度)对串扰的影响很大。对于同一布线结构,当电介质层的厚度增加一倍时,串扰明显加大。对于同样的电介质层厚度,带状传输线的串扰要小于微带传输线的串扰,由此可知,地平面对不同结构的传输线的影响也是不同的。因此在高速电路布线时,如带状传输线的阻抗控制能够满足要求,那么使用带状传输线可以比使用微带传输线获得更好的串扰抑制效果。

因此,在高速PCB板的布局布线中,可以注意以下方面,从而达到减小串扰的目的:

①加大线间距,减小线平行长度,必要时可以以jog方式走线,即对于平行长度很长的两根信号线,在布线时可以间断式地将间距拉开,这样既可以节省紧张的布线资源,又可以有效地抑制串扰;

②高速信号线在满足条件的情况下,加入端接匹配可以减小或消除反射,从而减小串扰;

③对于微带传输线和带状传输线,将走线高度限制在高于地线平面10 mil(1 000 mil=25.4 mm)以内,可以显著减小串扰;

④在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线,可以起到隔离的作用,从而减小串扰。

⑤在同一传输线的布线过程中,尽量减少过孔的使用,因为过孔的存在对传输线的特征阻抗会有较大的影响。

⑥在PCB布局布线设计中,尽量将连线较紧密的器件相互靠近,减小传输线的连线长度,同时还要利用时钟线的隔离、差分线对的等长、数据/地址总线的菊花连接方式等能带来较好信号完整性结果的措施。

2.4 降低电磁干扰

电磁干扰主要分为传导干扰和辐射干扰两大类,只要切断干扰源的产生源头和传播路径就能使电子设备符合电磁兼容性的要求。在PCB板的实际设计中,要注意以下几个方面的问题:

①在实际设计中建议使用实体地和电源层,避免电源和地被分割,这种分割可能导致复杂的电流环路。电流环路越大辐射也越大,所以必须避免任何信号,尤其是时钟信号,在分割地上布线。

②将时钟驱动器布局在电路板中心位置而不是外围。将时钟驱动器放置在电路板外围会增加磁偶极矩(magnetic dipole moment)。

③为了进一步降低顶层时钟信号线的EMI,最好在时钟线两侧并行布上地线。当然,最好将时钟信号布在地层与电源层之间的内部信号层上。

④时钟信号使用4~8 mil的布线宽度,由于窄的信号线更容易增加高频信号衰减,并降低信号线之间的电容性耦合。

⑤由于直角布线会增加布线电容并增加阻抗的不连续性,从而导致信号劣化,所以应该尽量避免直角布线和T型布线。

⑥尽量满足阻抗匹配。绝大多数情况下,阻抗不匹配会引起反射,而且信号完整性也主要取决于阻抗匹配。

⑦时钟信号布线不能与其他信号线并行走得太长,否则会产生串扰从而导致EMI增大。一个较好的办法是确保这些线之间的间距不小于线宽。