I2C接口用于I2C总线的驱动和接收,当I2C总线控制器为主机时,I2C接口必须按I2C总线规范驱动总线;当总线控制器为从机时,I2C必须能正确接收满足I2C总线规范的信号。I2C设计规范对总线的时序作了详细的定义,在不同模式下这些参数的具体数值都有明确的规定。“SCL/START/STOP 产生”状态机的状态转换如图4所示, I2C接口主状态机的转移图如图5所示。

4 仿真与硬件实现

本文中仿真工具采用Mentor公司的ModelSim Plus 6.0 SE,其显著的优越性能是提供了一个混合语言仿真环境,已在产业界广泛应用。为了测试验证系统的功能,本文采用了Atemel公司提供的采用I2C总线协议的AT24C02 E2PROM芯片(256B 8bit)的VerilogHDL仿真模型(AT24C02.v)作为从器件对象,用VerilogHDL语言构建了testbench(测试向量),对所设计I2C总线控制器进行仿真。

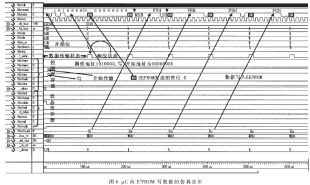

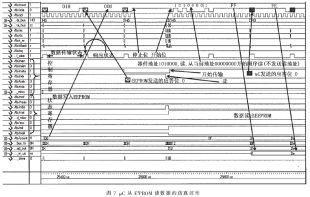

图6和图7为μC通过I2C总线控制器对E2PROM进行数据写/读的仿真波形(将数据FFH~0HH写进地址0~255单元,然后将它们再按顺序读的模式读出)。往E2PROM写入时需要给出所写起始单元的地址(图6中为00H); 从E2PROM顺序读时不用给出起始单元地址而从当前地址处开始读(本文中写完256B数据后,地址指针又回到0处)。相关状态及数据已在图中作了标示。由此可见,所设计的总线控制器完全符合标准I2C串行协议的时序要求。

本文设计的系统实现平台采用Xilinx公司的XC95216-10-PQ160 CPLD芯片,总逻辑门个数为4 800。经综合、适配、布局布线后占用器件资源的情况为:宏单元120/216(56%)、寄存器111/216(52%)、功能块331/432(77%)、乘积项分配器544/1080(51%)。可见,系统占用约一半的资源,相当精简。整个系统下载到CPLD后在2MHz时钟频率下运行正常。