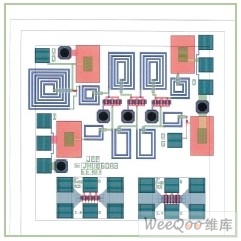

通过理想的仿真计算,该设计选用了6×30μm的增强型PHEMT器件,Craig Moore的198?年的设计中在MESFET管的漏极增加了一些额外的匹配元件,以保证有效输出电容和栅极输入容抗相同。此时输入和输出的集总参数传输线将是对称的,其相位延迟也相同。文章还比较了这种输入输出传输线对称的匹配方案和另一种漏级电容独立优化的方案(漏极电感和栅极不对称)。对于这个简单的3级PHEMT设计,栅极和漏极输入线的相移差别很小,这里就采用较简单的非对称方案。如果输入输出传输线的相位差较大,这种方案的就不能有效的合并各级的增益。下一步使用TriQuint公司提供的电感、电阻、电容以及互连线模型取代理想元件,进行更真实的仿真。图3显示了期望的最终放大电路的增益、匹配度、稳定因子和噪声系数。仿真中采用了30mA和3.3V的直流偏置设计,以限制其功耗在100mW以内,并实现了输出功率和三阶互调截止点的折中。图4是该电路的版图,同时还包含了两个有探针接入端的测试模型管:一个是设计中采用的6×30μm增强型PHEMT,另一个是普通的6×50μm耗尽型PHEMT。

图4:3级分布式放大器的版图(包括180μm栅宽的增强型测试建模管和一个300μm栅宽的耗尽型测试建模管)。

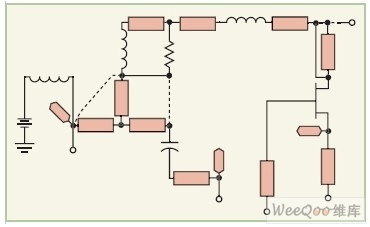

一个典型的分布式放大其中有一半的功率被输出传输线的50欧负载所吸收,为了提高输出效率,人们通常采用一些技巧,如渐缩型传输线方法。本设计采用了50欧姆输入输出线,为了减少DC功率的消耗,该传输线的一端的50欧姆终结负载和一个较大的电容(25pF)串联后,再通过通孔接地,这样既能保证射频信号接地,又能实现隔直流的效果。漏极较大的直流供电电流只流经低阻抗的电感元件,而不是50欧的终结负载(如图5),这样可以有效的减小50欧终结电阻上的功耗。这里漏极电感的大小也是一个重要的设计参数,该电感直接影响电路在1GHz附近的低频滚降速度,如果增大电容将会减小滚降速度,但是同时会增加串联电阻,从而提高直流功耗,而且较大的电感也会增大版图面积。

在提交产线流片之前,各设计还必须经过严格的设计规则检查DRC(design-rule check),自198?年第一次MMIC设计课程开始,约翰・霍普金斯大学就采用ICED(ICEDitor)软件,并采用TriQuint提供的DRC规则进行设计规则检查。另外还使用了“版图转电路图”LVS(Layout Versus Schematic)工具进一步比较从ADS中提取出来的网表是否符合ICED软件中的实际电气连接。有时设计虽然能通过DRC检查,但是仍然会有一些致命的错误,只有LVS工具才能发现这些问题。新版本的ADS已经具备内置的连接性检查功能,可以排除一些连接性错误,但是外部的LVS检测仍然是很有必要的。

图5:分布式放大器电路的直流等效电路,可以看出流经电感L35的电流只引起很小的压降。

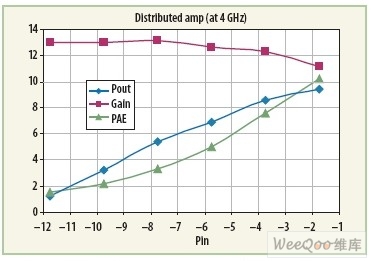

图6:实测的输出功率和效率结果。