本文讨论了高速串行链路中常用的 测试码型 伪随机码流的原理,以及不同的测试码型对物理层测试结果的影响。

高速串行总线的常用测试码型

在当今的电信和计算机产品上,相比传统的并行总线,电路中的串行总线越来越多,速率越来越快。比如通信产品中的10GBase-KR、CPRI2代,计算机中的PCIeGen2、SATA6G,存储产品中的SAS6G、FC8.5G,这些串行总线都陆续的跨过了5Gbps。由于速率比较高,使得串行总线上的相关的收发器芯片(SERDES)、连接器、单板、背板的设计面临着越来越多的挑战。对于这些高速串行总线的物理层测试,测试码型的选用至关重要,在很多串行总线的规范中对测试码型有严格的要求。本文将对此进行探讨。

首先,串行总线的物理层测试通常分为发射机测试和接收机测试,又称为TX测试和RX测试。发射机测试通常包括眼图、抖动、信号波形、幅度、上升下降时间等测试项目,接收机测试通常包括误码率、抖动容限、接收机灵敏度等测试项目。对于眼图测试、误码率和抖动容限测试,最常用的测试码是伪随机码(PseudoRandomBinarySequence,简称 PRBS ),主要有PRBS7、PRBS15、PRBS23和PRBS31。除了PRBS以外,K28.5、1010、CJPAT等码型在很多串行总线的物理层测试中都很常用,特别是计算机上的串行标准(比如SATA、USB3.0、SAS)的测试码型有所不同,在本文中主要讨论最常用的测试码型――PRBS。

PRBS的实现方法

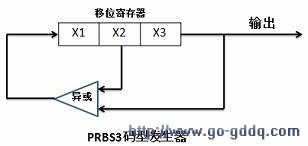

顾名思义,PRBS是伪随机码流,在其码流中包括了所有可能出现的比特组合,而且其出现的概率是相同的。PRBS信号是由PRBS码型发生器生成的。PRBS发生器通常是由线性反馈移位寄存器(LinearFeedbackShiftRegister,简称LFSR)和异或电路组成。如下图1所示为最简单的PRBS3的码型发生器,其多项式为X3+X2+1,即寄存器的第3位与第2位做异或(XOR)的逻辑运算后返回到寄存器的第1位,寄存器的第3位X3同时也是PRBS3发生器的输出。

图 1:PRBS3码型发生器原理

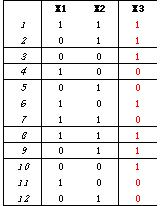

在表格1中显示了PRBS3的n个周期的时钟后输出n个比特的码流。X1/X2/X3分别是3个比特移位寄存器的低位到高位,输出位是X3,初始状态为X1/X2/X3=1/1/1,如表格第1行所示。

第1个时钟沿到达后,X3与X2异或后等于0,输入到X1,同时X1和X2前移到X2和X3,所以X1/X2/X3=0/1/1,如表格第2行所示;

第2个时钟沿到达后,X3与X2异或后等于0,输入到X1,同时X1和X2前移到X2和X3,所以X1/X2/X3=0/0/1,如表格第3行所示;

第3个时钟沿到达后,X3与X2异或后等于1,输入到X1,同时X1和X2前移到X2和X3,所以X1/X2/X3=1/0/0,如表格第4行所示;

……

以此类推,第5行为0/1/0,第6行为1/0/1,第7行为1/1/0,第8行为1/1/1,与初始状态相同,接下来的第9行和第10行与第2行和第3行完全相同,也就是说PRBS3的码型输出7个比特后开始重复。X3是PRBS3的输出位,所以PRBS3输出的码型为1110010,码长为7,如图2所示,每7个比特后开始重复输出同一码型。在PRBS3中包括了11100属于码流中频率最低的码型,010是频率最高的码型。

表格1:PRBS3的3位寄存器数值

图2:PRBS3输出信号

为何PRBSN的码长为2^N-1

在PRBS3的3位寄存器可以产生2的3次方合计8个排列组合。采用XOR异或电路的PRBS发生器在3个比特都是0的时候,下一个时钟到来的时候,第3个比特和第2个比特异或后还是0,输入到寄存器的第一位还是0,同时第1个和第2个比特前移到第2个和第3个比特,这样,移位后寄存器的3个比特都是0,则PRBS发生器的输出一直都是0,被锁住。所以PRBS3码流中不能出现3个全0的比特,这样,PRBS3的组合方式为2^3-1=7共7种,码长位7个比特。同理,PRBS7的码长为2^7-1=127个比特,PRBS15的码长为2^15-1=32767个比特。