摘要 选用了一种基于DSP与FPGA结构的新型射频扫频仪的设计方案,重点讨论了其扫频信号源的设计。分析了频率合成技术的发展趋势,介绍了PLL技术和DDS技术的原理,并在此基础上给出了以PLL+DDS方式实现的扫频信号源设计。

关键词 DSP;扫频仪;PLL;DDS

频率特性分析仪即扫频仪是在示波器基础上发展起来的一种频率特性图示仪,在工程实践和科学实验中都有着广泛的应用,是现代信息产业中一种重要的电子测量仪器。随着现代电子信息技术的飞速发展,扫频仪也向着数字化、小型化、智能化的方向发展。DSP、FPGA等技术的应用,解决了传统扫频仪体积庞大、操作繁琐、分立元件多、价格昂贵等问题。

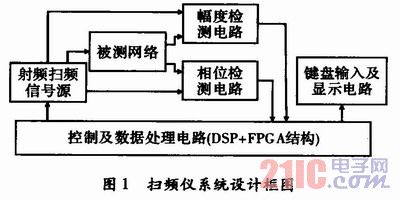

1 扫频仪系统设计

该系统的设计主要由控制及数据处理电路、扫频信号源电路、幅度检测电路、相位检测电路、键盘输入及显示电路构成。控制及数据处理电路采用DSP+FPGA的结构设计,DSP具有强大的数据处理能力、较高的运行速度和稳定的性能,而FPGA容量大,灵活性强,能够进行编程、除错、再编程和重复操作,可以充分地进行设计开发和验证。因此由DSP芯片和FPGA可编程逻辑器件所组成的控制及数据处理模块外围电路少,运算速度快。

DSP作为主控芯片完成整个系统的控制及采集后的数据处理,FPGA的应用使DSP接口控制简单容易实现。编写DSP程序,可以设置频率起止点和步进,完成频率扫描。

2 DDS+PLL结构频率合成法原理

2.1 频率合成技术

频率合成是由一个或几个参考频率源产生一个或多个频率的系统元件的组合。随着技术的进步,尤其是迅速发展的通信领域对于频率精度和稳定度的要求越来越高,频率合成技术也受到了越来越多的挑战。总地来说,频率合成技术的发展经过了3个阶段:(1)直接频率合成技术;(2)锁相频率合成技术(PLL);(3)直接数字频率合成技术(DDS)。

直接频率合成由于采用了大量的混频、分频、倍频和滤波,使得频率合成器体积庞大、成本高、不易调试、指标难以达到需求,已逐渐被模拟或数字锁相环频率合成技术代替。