・上一文章:等效电路法在放大电路分析中的应用

・下一文章:基于ADVISOR的电动汽车动力性能仿真分析

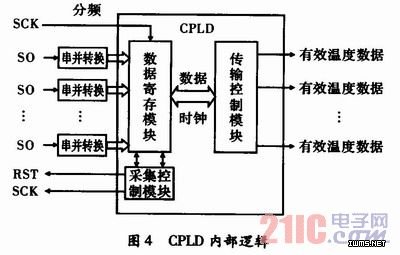

3 CPLD内部逻辑

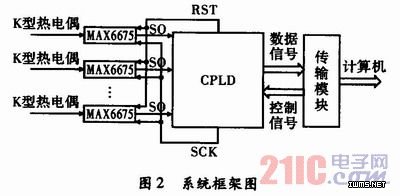

如图2所示,K型热电偶将采集的模拟信号传送给MAX6675,再由它转化成数字信号传入CPLD,CPLD根据MAX6675芯片的时序进行数据处理得到需要的信号,最后由传输模块传到计算机进行数据显示和统计、处理。所以本文的重点工作便在CPLD内部逻辑的设计。在进行内部逻辑设计之前,须了解MAX6675的工作时序与原理:当CS引脚由高电平变为低电平时,MAX6675停止任何信号的转换,并在时钟SCK的作用下向外输出已转换的数据;当CS引脚从低电平变到高电平时,MAX6675将进行下一轮数据的转换。一个完整的数据读取需要16个时钟周期,数据的读取在SCK的下降沿进行。MAX6675的工作时序图如图3所示。

如图3所示,根据芯片手册tcss是CS下降到SCK上升的时间,规定其最小值为100 ns,tCH+tCL为SCK的一个时钟周期,规定最小周期为200 ns,tDV为CS下降沿到数据输出的时间,规定最大不超过100 ns。tDO为SCK下降到输出有效数据的时间,tTR为CS上升沿到数据停止输出地时间,规定最大值均为100 ns。根据这些手册上的这些时间规定,在设计CPLD内部逻辑电路时便严格按照要求,将SCK时钟周期设为1 000 ns即1 MHz,tcss设为1 000 ns,tDVtTR都设为100ns。图中还可以看出SO是16位的输出数据,其中只有D14~D3位为温度数据,D15位为无用位,D2位为热电偶断线测试位,D1位为MAX6675标识符,D0位为三态,所以从16位数据中取出D14~D3这12位数据进行转换和处理。基于以上分析,设计了如图4所示的内部逻辑模块。