2.1 脉冲发生模块

脉冲发生模块和计数模块均由CPLD逻辑电路实现。CPLD选用ALTEra公司MAX II系列EPM240T器件,支持高达300 MHz的内部时钟,其速度可以满足测量需求。

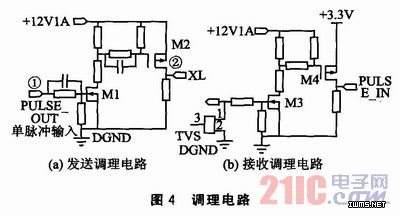

脉冲发生模块由脉宽设置单元、脉冲输出单元组成。为节省单片机I/O口资源,脉宽设置由一组16位串入并出移位寄存器实现,当单片机资源足够时,可省去该单元。脉冲输出单元由状态机实现,如图2所示。

其中,clk_50m为时钟输入端,pulse_with为脉宽设置端口,pulse_out为脉冲输出端口,enalble为使能输出端口。当enable=1时,pulse_out输出一个高电平,其宽度为Tclk_50m×(pulse_with+1)。例如pulse_with=0,脉宽默认值为t=Tclk_50m×(0+1)=20 ns。设置不同的pulse_with,输入脉冲宽度可调,这样可以在测量不同长度的线缆时调整脉冲宽度,使测量结果更加准确。

如图3所示,计数模块由一个16位计数器和一个16位并入串出移位寄存器电路实现。enalble使能端用于防止干扰脉冲输入启动计数器;start_counter为使计数器启动和停止的脉冲输入,上升沿有效;clk_50m为计数器时钟,该时钟影响测量精度,其频率越高,线缆的测量误差范围越小;Q为计数值输出;EOC为计数结束标志。

计数器的启动由入射脉冲触发,停止由反射脉冲触发,计数值由Q数据接口输出,计数停止后输出高电平。单片机查询计数结束标志EOC,当电平为1后读取计数值。

2.2 调理电路

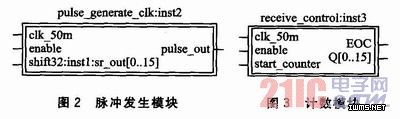

2.2.1 发送调理电路

发送调理电路由放大电路组成,如图4(a)所示。场效应管M1将输入的正脉冲转换为最大值为12 V的负脉冲,再经M2反相后,即可注入到被测电缆和接收调理电路。这里选用MOS管而不是运放芯片实现信号脉冲的放大、反相,便于节省成本,缩短信号的传输延时。