1.5 输出滤波电容的计算和设计

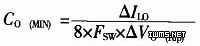

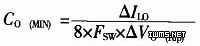

输出滤波电容要考虑工作频率,纹波大小,电容的ESR及ESL,由于有源箝位工作在200kHz之下,又考虑到成本,所以必须选择优质的低ESL及ESR铝电解电容,减小每个电容的容量,增加并联电容的数量,由于工作频率的提升已经比67.5kHz的方案少用一半容量的电容,因此上策是数量不变,减小单个容量,大约减一半左右。

这是最小的限定值,实际应该参照ESR、ESL大约加出50~80%,应对负载的变化,限制瞬态电压不超过3%,则有:

为了减小噪声,在电解电容的最终点要加入一支瓷片电容消除噪声,容量为10μF左右。

1.6 功率变压器的设计

功率变压器的设计计算与硬开关状态的计算方法完全一致,再测出Lm,Lr。接入电路后,先串入外部电感Lr,调好功率MOS的ZVS状态后,取下外串电感Lr,加入气隙达到与试验相同的主功率MOS的ZVS状态,记录此时变压器的Lm及Lr,以上即为设计结果。变压器的导线切记f=200kHz,而不能选择d超过0.27mm的导线。大电流时宜选择铜箔,铜箔应纵向切开缝隙减少涡流损耗。在磁芯磁密选择时考虑到200kHz频率,B值不宜超过2200高斯。

2 箝位电容MOS及相关元件的设计

变压器驱动法,IC驱动法可参考L6384的驱动设计。

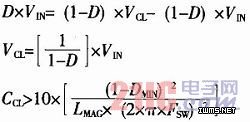

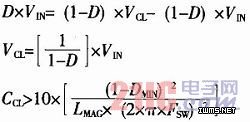

对于箝位电路,核心是令变压器磁芯完全复位,使其工作在第I和第Ⅲ象限,这里主要按伏秒积考虑。

箝位电容较大时,主功率MOS耐压可以降低,箝位电容较小时,变压器复位时间较长,按工作频率及主功率MOS的波形,做最后调试决定。

3 功耗计算及效率预估

3.1 主功率及箝位MOSFET的功耗

选定主功率MOS之后,查出其RSDON,工作在ZVS状态,主要功耗为导通损耗。

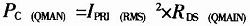

但是其Coss充放电造成的谐振损耗是拿不掉的,应该计算。其计算式为:

式中,VCL为箝位电容上的电压最高值。驱动损耗的发热在驱动器部分不在MOS上。实际上因为达不到绝对的零开关损耗,实际损耗比上述计算值要大出10%左右。

箝位MOS的功耗更难于计算,可按主功率MOS功耗的30%来估算。

上一页 [1] [2] [3] 下一页