3.2 同步整流MOS QF的功耗

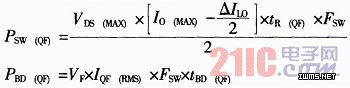

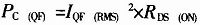

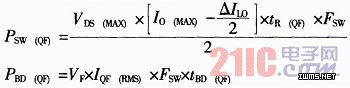

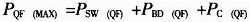

在最坏条件下,QF功耗主要为导通损耗,其次为开关损耗。

开关损耗为开启损耗及体二极管反向恢复损耗,两项加在一起可按导通损耗的50%估算。

3.3 回流MOS QR的功耗

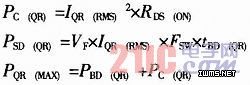

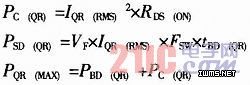

在最坏情况下,QR的功耗主要为导通损耗及体二极管反向恢复损耗。

3.4 其它损耗

(1)功率变压器的损耗

功率变压器损耗的计算很繁锁,为简化设计按总功率的1.5~1.8%估算,其损耗来源为铜损及铁损,铜损由导线电阻造成,若是铜箔还有涡流损耗。铁损即磁芯损耗,主要为磁滞损耗及涡流损耗。

(2)输出滤波电感的损耗

输出滤波电感的损耗与变压器类似,主要是铜损及铁损,按总功率的0.5~0.8%考虑估算。

(3)输出滤波电容的损耗

输出滤波电容的损耗主要为在开关频率下的ESR、ESL以及电解电容的漏电造成,此部分开始估算时可以忽略。

(4)控制电路的功耗

控制电路的功耗包括初级的控制IC静态功耗,对主功率MOS,箝位MOS的驱动功耗,对同步整流MOS的驱动功耗,反馈放大器及光耦部分的功耗,可按0.5%的总功耗估计。

4 其它设计

4.1 PFC设计

PFC按CCM方式设计,建议选择ICE1PCS01或NCP1653。工作频率建议选为PWM的一半,若能令两者同步更为可取。主要求出升压电感L,升压二极管D,主功率MOSFET-Q的选择及功耗计算,Bulk电容的计算和选择。

对于PCB设计,由于有源箝位方式的工作频率比双晶正激电路高一倍多,所以它的PCB-Layout要给予更多的关注。可按照PFC、PWM控制IC的应用注意认真处理。

4.2 输出设计

对于5V及3.3V的输出设计,建议选择Post Regulator方案,当然按成本考虑也可以采用磁放大器:在反馈系统设计时,建议选择开环增益更高的运算放大器LM358。

上一页 [1] [2] [3]