m序列的两位控制数可以表示为m2m1,则整个频率集肚的跳变规律描述如下:

设传输的数据经编码后为D2D1,当前频点为q,则下一跳频点q’为:

![]()

在满足表2控制关系的基础上,如果第刀跳与第n-2跳的频点相同,则放弃当前m序列的控制作用,将跳频子集变换,用(q’+N/4)modN代替q’的值。

2 短波差分跳频系统的信号发生器的设计

2.1 短波差分跳频信号发生器的整体设计

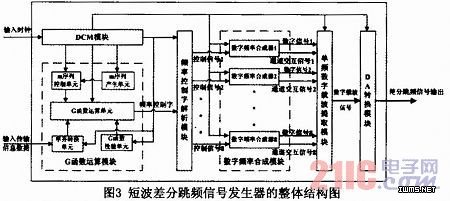

差分跳频信号发生器的功能为根据传输信息数据、前一跳的差分跳频信号频率控制字、m序列和G函数规则产生当前跳的跳频频率控制字,由跳频的频率控制字来控制数字频率合成器,产生对应频率的数字差分跳频信号,最后通过DA转换模块变为模拟差分跳频信号输出。

根据差分跳频信号产生模块的功能,并结合FPGA平台的器件特性,设计的短波差分跳频信号发生器的整体结构如图3所示。

从图3可以看出差分跳频信号发生器共包含6个关键模块:DCM模块、G函数运算模块、频率控制字解析模块、数字频率合成模块、单频数字载波提取模块和DA转换模块。各模块相互协作,共同实现差分跳频系统信号发生器的功能。其中,DCM模块为其他各模块、各单元提供不同的时钟驱动;DA转换模块将数字差分跳频信号变为模拟差分跳频信号输出。其他关键模块的设计将在下一节做详细讲述。

2.2 短波差分跳频信号发生器的关键模块设计

2.2.1 G函数运算模块

G函数运算模块共包括5个功能单元:串并转换单元、m序列产生单元、m序列控制单元、G函数运算单元和G函数校验单元。

串并转换单元对输入数据进行处理,由于数据每次只有1bit输入,因此输入数据经串并转换单元后,可以变为每次传输2bits或4bits数据。

m序列生成单元利用多级线性反馈移位寄存器生成m序列。

m序列控制单元将每次选取m序列的两个最高位作为m序列控制位,控制差分跳频信号频率控制字所在的子集。

G函数运算单元根据G函数规则、m序列的两位控制位、传输的数据信息以及前一跳的跳频频率控制字,产生当前跳的跳频频率控制字。

G函数校验单元判断第n跳和n-2跳的跳频频率控制字是否相同,如果相同,则放弃当前m序列的控制作用,将跳频子集变换,用另一个规则产生当前跳的跳频频率控制字。

2.2.2 数字频率合成模块

数字频率合成子模块共包含8个数字频率合成器,用来产生不同频率的数字载波信号。差分跳频信号产生逻辑控制模块根据差分跳频信号频率控制字产生对应数字频率合成单元的控制信号,为节省输入输出端口,在控制信号和时钟驱动信号的控制下,1个数字频率合成单元产生的不同频率的数字载波信号经过时钟交叠合并为一路数字信号,同时生成一个通道交互信号,差分跳频信号产生逻辑控制子模块根据频率控制字所指定的单一频率的数字载波信号所在通道,按通道交互信号进行单一频率数字载波信号的提取。

2.2.3 频率控制字解析模块和单频数字载波提取模块

频率控制字解析单元在输入时钟的控制下,将频率控制字解析,产生数字频率合成器选择控制信号和通道选择控制信号,同时将通道选择控制信号发送给数字载波信号合并控制单元。数字载波信号合并控制模块通过通道交互信号、数字频率合成模块输出的数字信号和通道选择控制信号,在时钟的驱动下,将数字载波信号合并为一路信号输出。最后将数字信号输出发送给DA转换模块,将其变为模拟信号。