ICS8442的性能参数如下:

输出信号频率范围为31.25~700 MHz;晶振频率范围为10~25 MHz;VCO频率范围为250~700 MHz;

ICS8442是LVDS逻辑电平,具有极低的相位噪声,这种特性使它非常适合用来为吉比特以太网或同步光纤网提供时钟信号。

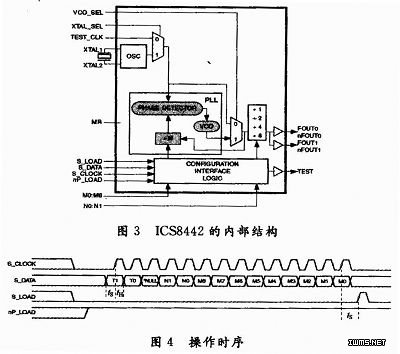

ICS8442的内部结构图3所示。ICS8442内部有一个完整的PLL锁相环,其VCO的输出频率范围在250~700MHz之间,倍频系数是由M决定的,M的取值范围在10~28之间。VCO的输出频率为:

![]()

ICS8442最终的输出结果还要经过一个分频器N,最终输出结果的频率和晶振输入频率的关系式为:

![]()

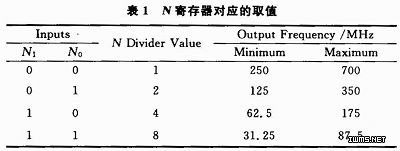

中:N是一个2位的寄存器,其对应的取值如表1所示。

对ICS8442时钟芯片的操作主要是对寄存器M,N的写操作。ICS8442支持并行写操作和串行写操作,根据硬件电路的设计,程序采用串行的写操作时序。当ICS8442的nP_LOAD置为高电平和S_LOAD置为低电平时,芯片实现串行操作。操作时序如图4所示。

当S_LOAD置为低且nP_LOAD置为高之后,数据在S_CLOCK的上升沿处寄存在缓冲器中,在S_LOAD的下降沿处将数据锁存到寄存器M,N中。

由于AURORA光纤通信的输出时钟频率设定的是125 MHz,结合硬件电路的设计,硬件晶振的频率为20 MHz,因此选择M值为000011001(25),N的值为10(4),故时钟芯片的时钟输出频率为:

![]()

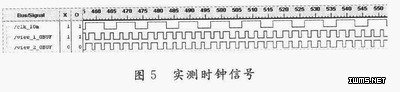

时钟控制模块的实测时钟信号如图5所示。

图5是用Chipscope在线逻辑分析仪得到的波形,由于Chipscope在线逻辑分析仪的触发时钟是100 MHz,因此在抓取125 MHz的时钟信号时,在图上显示的时钟信号占空比不定,若将时钟芯片产生的时钟频率降低,则此现象消失。

2.2 AURORA发送模块

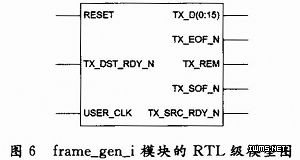

在生成AURORA IP CORE时,同时生成了一个基于AURORA协议的例示程序。因此,要实现基于AURORA协议的光纤通信,在发送端只需要在frame_gen_i模块将要发送的数据打包,然后通过AURORA模块发送出去。因此该模块着重介绍如何将上一级传送过来的数据进行打包压缩,形成适合AURORA协议的数据帧,通过AURORA协议发送到接收端。图6为frame_gen_i模块的RTL级模型图。

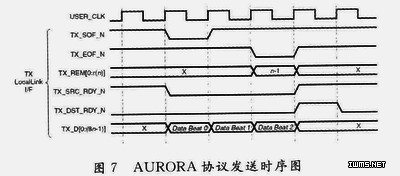

考虑到上一级传输数据速率可能会与AURORA传输的时钟频率不同,因此在发送端建立一个FIFO来做缓冲器。并且AURORA协议的发送时序图如图7所示。可以看出,TX_SOF_N为数据包帧的开始标志,TX_EOF_N为数据包帧的结束.标志,TX_REM[0:r(n)]记录最后的传输数据的线程,TX_SRC_RDY_N为低代表数据有效,TX_DST_RDY_N为低代表准备好接受数据,TX_D[0:(8n-1)]是此模块的输出数据。以上信息是AURORA协议的发送时序,在使用FIFO做缓冲时也应该遵循这样的协议。