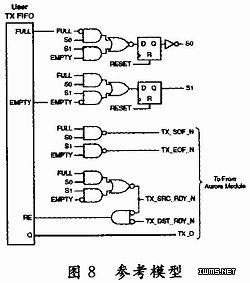

发送端的FIFO模块分别包括FIFO的复位信号、FIFO空、FIFO满、以及读/写时钟、使能和数据信号线。因此应该根据FIFO的标志位empty和full来产生AURORA的发送时序,参考模型如图8所示:当RESET信号到来之时,首先将S0置为高电平,将S1置为低电平,同时根据FULL和EM-PTY的状态确定接下来的S0和S1的状态,进而根据以上逻辑关系得到TX_SOF_N,X_EOF_N,TX_SRC_RDY_N等逻辑信号,并且根据数据X_DST_RDY_N和TX_SRC_RDY_N生成FIFO的读使能。由以上逻辑可以看出,只有在FULL为1,EMPTY为0时,FIFO的读使能才能被打开。TX_SOF_N为数据包的帧头标志,TX_EOF_N为数据包的帧尾标志,TX_STC_RDY_N为低时代

表数据有效,TX_DST_RDY_N为输入信号,根据此输入信号确定FIFO的读写时序。

对FIFO时序操作需要根据上述电路图所产生。在上述电路图中,有一个D触发器,其RESET信号是复位信号,复位既是将触发器输出端口清零,即将S0置1,将S1置0。在之前的程序中误将这里写反,即RESET信号到来之后,将S0置0,S1置1。这样导致的结果是在最开始输入的一段数据丢失,之后的结果输出正常。经过仿真分析之后检查出问题并已改正。

2.3 AURORA接收模块

同样在AURORA协议模块中,要实现对数据的接收,只需在frame_check模块中对接收的代码加以修改,增加自己所需要的内容,完成对数据的解码提取,剔除冗余信息,并完成数据的缓存。

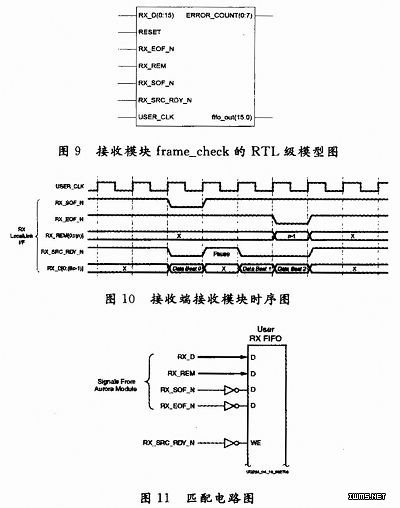

接收模块frame_check的RTL级模型图如图9所示:其中,RX_D为接收端接收的缓存于FIFO的数据,REsET为复位信号,RX_EOF_N为数据包帧尾的标志,RX_SOF_N为数据包帧头的标志,TX_SRC_RDY_N为低时代表数据有效,USER_CLK为系统时钟。fifo_out为数据缓存的输出,ERROR _COUNT为系统检错输出结果。因此在接收端接收模块的时序图如图10所示。根据该时序图可以确定接收时序,同样,在AURORA协议末端,由于与下一级系统的速率可能不匹配,因此需要在接收末端加上一个FIFO做缓存,同样其电路图如图11所示:根据RX_SRC_RDY_N生成FIFO的写使能信号,该发送模块设计完毕。

3 测试分析

3.1 功能测试

在基本功能测试中,主要测试光纤模块传输是否正确。由于光纤模块共有A,B,C,D四个通道,对每个通

道都要进行读/写测试。将通道A作为数据发送端,通道B作为数据接收端,应用光纤将A,B两端进行联通,然后将应用程序数据写入A通道FIFO中,当FPGA接收到到数据后,将A通道数据通过光纤传输到通道B接收缓存中,然后通道B将数据发送到上位机,从而形成一个环路。比较发送和接受端的数据,可以验证数据传输的正确性。同理可以将此方法应用于四个通道中的任意两个作为发送端和接收端,从而验证并测试传输功能。

3.2 性能测试

性能主要对其传输速度和传输误码率进行测试。就传输速度而言,主要由FPGA控制,在其内部设置了两个初始值为0的计数器,在PCI-Express开始传输数据时,FPGA开始计数读/写数据包和发送数据包的个数,然后每隔一段时间将计数值写入两个计数寄存器中,并将原有值替换,为了精确速率,可以缩短计数时间,并多次测试取平均值,就可得到传输瞬时速度。经测试:PCI-Express接口的传输速度在600MB/ s,光纤传输在850 MB/s,满足设计要求。对于误码率的测试,主要使用误码分析软件对其误码性能进行测量,设计由上位机和PCI-Express接口,光纤通道组成数据传输环路,通过不同的指令和要求验证传输正确性,当数据包大小在4 Kb,8 Kb,16 Kb,32 Kb,测试数据长度分别为1 000 Kb,1 000 000 Kb,100000 000 Kb时,错误率都为0 b,误码率满足设计要求。

4 结语

该设计系统以Virtex-5为核心构建的平台,对AURORA协议下串行传输系统进行了设计与实现。通过对核心问题的解决,将计算机与外部扩展很好的结合,达到信号传输的高速、稳定的目的。实验证明,板卡设计的整体思路和核心方法的解决是完备的,并使得板卡的传输速率和稳定性的到了较大的提高。