序言

随着全球范围内的海量数据对无线和有线网络的强大冲击,运营商面临着严峻的挑战,他们需要不断推出既能满足当前需求也能满足未来需求的网络。因此,通信基础局端设备制造商在致力于降低每比特成本和功耗的同时,也在不断寻求能够满足当前及至未来需求的核心技术。TI最新推出的新型 KeyStone 多内核 SoC 架构能够游刃有余地满足这些挑战。

基于新型 KeyStone 多内核 SoC 架构的器件集成了多达 8 个TMS320C66x DSP CorePAC,能够实现无与伦比的定点与浮点处理能力。KeyStone 架构经精心设计,是一款效率极高的多内核存储器架构,允许并行执行任务的同时,还能使所有的 CorePac实现全速处理。本文探讨了 KeyStone 存储器的层级结构,及其将如何与 SoC架构的其他组件进行连接以实现多内核全速处理。

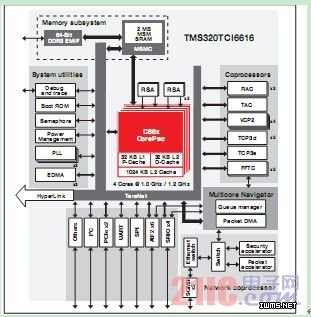

德州仪器 (TI) 积极创新,努力迎接多内核 SoC 技术带来的挑战。TI KeyStone 架构拥有众多组件,其中包含全新的 C66x 定点和浮点 DSP 内核、可实现基于标准的优化功能和接口的可配置协处理器、层级存储器架构、TeraNet 交换结构以及可将上述各组件连结在一起的多内核导航器。KeyStone 架构具备三个存储等级。每个 C66xCorePac 均拥有自己的一级程序 (L1P) 和一级数据 (L1D) 存储器。另外,每个 CorePac 还拥有局域的二级统一存储器。每个局域存储器均能独立配置成存储器映射的SRAM、高速缓存,或是两者的组合。

KeyStone 架构包含共享的存储器子系统,其由通过多内核共享存储器控制器 (MSMC) 连接的内部和外部存储器组成。MSMC 允许CorePac动态地分享程序和数据的内外部存储器。

图 1 - KeyStone 器件方框图 - TMS320TCI6616

2

MSMC 的内部 RAM 允许各部分被配置成共享的二级 RAM 或者共享三级 (SL3) RAM,从而可为程序员提供高度的灵活性。SL2 RAM 仅能够在局域 L1P 和 L1D 高速缓存中缓存,而 SL3另外还可在局域 L2 高速缓存中进行缓存。

为向软件执行提供快速通道,外部存储器同内部共享存储器一样,通过同一存储器控制器进行连接,而并非像在嵌入式处理器架构上所进行的传统做法那样,与芯片系统实现互通互连。外部存储器始终被看作是 SL3 存储器,并可在 L1 和 L2 中缓存。接下来的我们将探讨在KeyStone 架构中实现的各种性能增强。

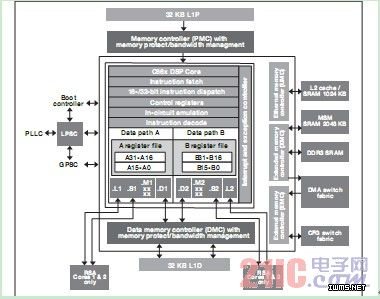

存储性能增强 C66x CorePac 的内部存储器架构与此前 C6000™ DSP 系列产品相比,主要在四个方面实现了增强,而这突出体现在性能指标和实用性方面。这些改进旨在实现如下优势:1) 无论多个内核和数据 I/O 是否处于高度繁忙状态,都能提高存储器各级的执行效率;2) 更轻松便捷地管理多个内核和数据 I/O 之间的缓存一致性;3) 存储器的保护与地址扩展,以及;4) 将对软错误的保护进一步扩展至较高级别的存储器。

执行效率 —— C66x CorePac 的存储器子系统在功能上与最新的 C64x+™ 和C67x™ 系列 DSP 系列 C64x+™ 和 C67x™ 的相当。每个局域 L1存储器均为 32KB,并能够配置成全速缓存(默认)、全存储器映射 SRAM,或是 4、8 或 16KB 高速缓存选项的组合。L1P 始终为直接映射,而 L1D 则始终为双向集关联 (two-way set-associative)。

图2 – CorePac 存储器增强