・上一文章:读码器系统用于太阳能电池制造的实现

・下一文章:计算电磁学在电磁兼容仿真中的应用

4 实例设计过程与仿真

4.1 FIR系数提取

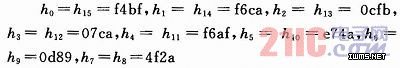

利用Matlab中Fdatlool设计一个16阶低通FIR滤波器,各项性能指标为:采用频率fs=48 kHz,截止频率fstop=12 kHz,通带宽度FPass=9.6 kHz。系数数据宽度为16位;输出数据宽度是16位。为了便于FIR滤波器的FPGA实现,减小误差,将Fdatlool提取的滤波器的系数量化取整后为:

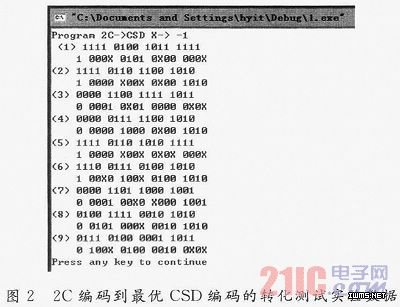

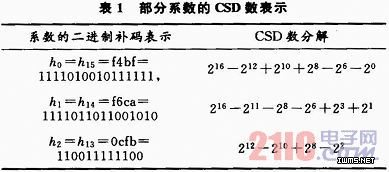

4.2 系数的CSD转换

读入量化系数,进行CSD转换操作,生成CSD码,表1是部分量化后的系数及对应的CSD数。

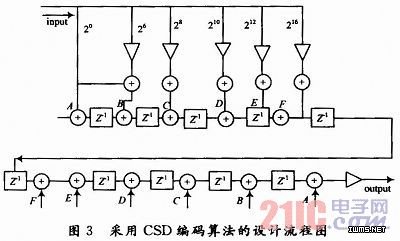

4.3 FIR滤波器实现结构

采用转置形式的FIR滤波器结构,此结构和直接型结构不同的是,输入信号X[n]是同时分别和滤波器系数向量相乘,不需要通过不同的延时单元再和相对应的滤波器系数相乘。这种结构最大的优点是工作频率较高,图3给出了采用CSD编码算法的设计流程图。