・上一文章:读码器系统用于太阳能电池制造的实现

・下一文章:计算电磁学在电磁兼容仿真中的应用

5 基于FPGA的FIR试验结果

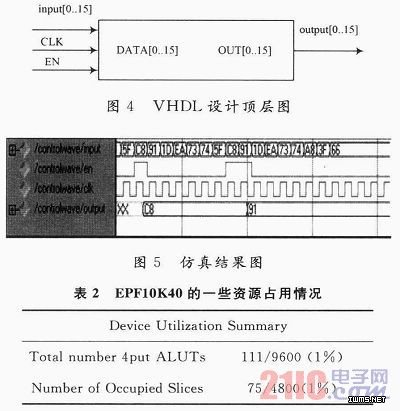

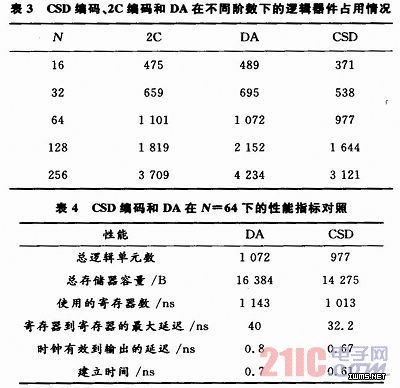

为验证本文提出的算法的普遍性,以并行DA和2C编码方式设计了一系列阶数从16到256阶的FIR滤波器,滤波器在ALTEra公司的开发软件Max+PlusⅡ中进行编译和布局布线,采用的目标器件为EPF10K40芯片,在系统中对3种实现结构进行测试,测试数据位宽为8位。通过表3的比较结果可以看出,使用CSD编码,资源耗用明显下降。当FIR阶数很高,系数很复杂时,CSD编码的优势会更加显著。表4给出了N=64时DA算法和CSD算法的具体性能指标,从结果来看,CSD编码相对于单纯的DA在系统资源和整个系统延迟上有明显的提高。

6 结语

滤波器用VHDL硬件描述语言实现,采用Altera公司的EPF10K40芯片,在Max+PlusⅡ中进行了仿真验证。从结果来看,文中所提出的CSD编码算法,具有一定的研究价值和实用价值,CSD编码在处理序列较多的情况下,在资源占用、速度处理方面的效果尤为明显。采用CSD编码方式对FIR滤波器进行优化设计,可减少FIR实现的FPGA资源消耗。