・上一文章:基于OPA820宽带放大器的设计

・下一文章:无线传感器网络节点节能管理方式的研究

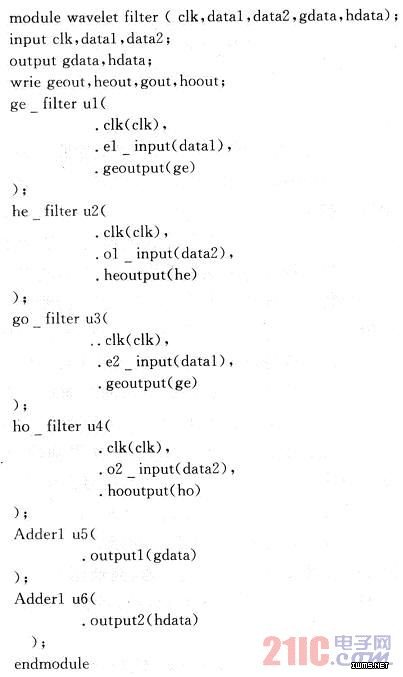

下面对双正交小波滤波器用VerilogHDL进行顶层设计:

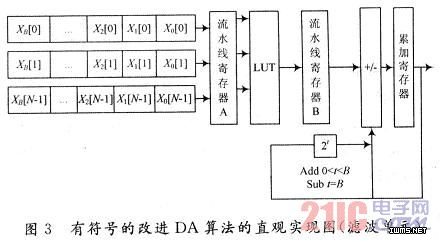

对于双正交小波滤波器的部件Ge,Go,He,Ho设计,采用行为描述方式进行设计。VerilogHDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL级的模型设计。在Veril—ogHDL语言中行为描述分为算法和RTL两种。算法级:用语言提供的高级结构能够实现算法的运行模型。RTL级:描述数据在寄存器之间的流动和如何处理,控制这些数据的流动,采用改进的DA算法(如图3所示)。DA算法完成一次滤波所需要B次的累加也就是B个时钟周期完成一次运算,B位输入数据的位宽。它的查找表(LUT)的大小是由滤波器的阶数N决定的,共需要2N个查找表单元,如果系数N过多,用单个LUT不能够执行全字查找则可把系数分组,利用部分表并将结果相加,为了简单的阐述算法,在此系数只分了2组,每个单元的位宽是由滤波器的系数的量化决定的。Ge,Go,He,Ho四个滤波器虽然长度不同,但具有相同的电路结构,如图4所示。