摘要:针对跳频通信系统有固有噪声的特点,结合DDS+DPLL高分辨率、高频率捷变速度的优点,并采用ALTEra公司的Quartus-Ⅱ_10.1软件进行设计综合,提出了一种新型的跳频信号源。结果表明,该设计中DPLL时钟可达到120 MHz,性能较高,而仅使用了30个LUT和18个触发器,占用资源很少。

关键词:数字鉴相器;滤波器;数控振荡器;DPLL

引言

军事通信中,常采用跳频技术来实现通信信息的保密和抗干扰,尤其是应用在通信系统中抗跟踪式干扰方面,它是电子对抗中非常重要的一个研究课题。

最初的频率综合器全由模拟电路实现,由于模拟电路存在温度漂移、电网电压等缺点,给系统的同步带来困难。随着大规模、超大规模数字集成电路的发展,在部分应用领域,数字频率综合器逐渐取代了模拟频率综合器。近年来随着FPGA和CPLD技术的迅猛发展,数字频率综合器的实现方式和工作速度都到了本质的改进和提高,可以说数字频率综合器是随着FPGA的发展而发展起来的。

1 各个功能模块的组成原理与实现

1.1 数字鉴相器

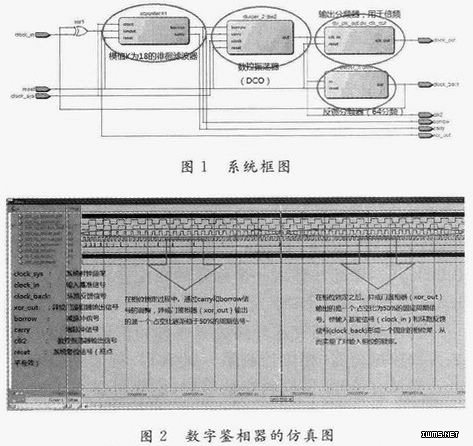

在数字鉴相器(异或门鉴相器)中,首先将输入信号与本地估算信号进行比较(其中,输入cLOCk_in基准频率与clk2反馈回来的频率相同,只存在相位差),从而得到一个表明相位误差的脉冲输出,实际上就是一个异或门。系统框图如图1所示,仿真结果如图2所示。

![]()

从仿真波形中可以看出:当系统对频率进行锁定的过程中,使可变模计数器产生增脉冲(carry)和减脉冲(borrow)信号,鉴相器输出(xor _out)的是一个逐渐趋于占空比为50%的方波,从而使输入基准频率与反馈频率锁定在一个固定的相位上。

1.2 徘徊滤波器

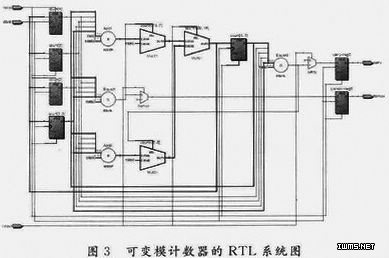

徘徊滤波器的作用是平滑鉴相器带来的相位抖动,选用双向计数器来实现该功能,其RTL系统构架如图3所示。在PLL工作过程中,环路锁定时,异或门鉴相器的输出XOR_OUT是一个占空比为50%的方波。因为在DPLL的基本结构中,K变模可逆计数器始终起作用。因此当环路锁定后,如果模数K取值较小,K变模可逆计数器会频繁地周期性输出进位脉冲信号CARRY和借位脉冲信号BORROW,从而在脉冲加减电路中产生周期性的脉冲加入和扣除动作,这样就在脉冲加减电路的输出信号XOR_OUT中产生了周期性的误差,称为“纹波”;如果模数K取值足够大(对于异或门鉴相器,K应大于M/4),则这种“纹波”误差通过除N计数器后,可以减少到N个周期出现一次。也就是说K变模可逆计数器的进位脉冲信号CARRY和借位脉冲信号BORROW的周期是N个参考时钟周期。只有当本地枯算信号与输入信号的相位误差在同一极性持续增加时,计数器会朝一个方向计数,直到有进位或借位脉冲输出。该脉冲即是数控振荡器的控制信号,用以控制数控振荡器输出的本地估算脉冲的频率与相位。由此可见,由于徘徊滤波器的作用,使得锁相环只有在本地估算信号与输入数字的相位有一定的误差时,才进行调整,以达到平滑噪声干扰带来的相位抖动的目的。

![]()

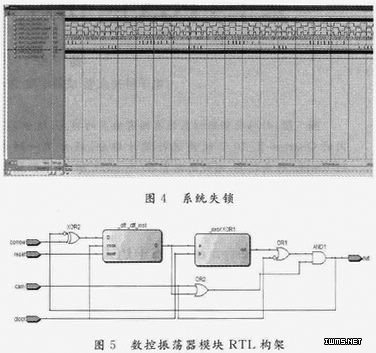

若系统失锁,如图4所示,则异或门鉴相器(xor_out)输出的不是一个占空比固定的周期信号。从而使反馈的信号(clock_back)无法跟踪输入的基准信号(clock_in),即无法形成一个固定的相位差。