(1)FPGA逻辑运算中心。用来接收其他各部分的数据,并按照程序中设定的方案对所收到的数据进行相应的分析和处理。包括:对从MCU接收来的数据指令进行分析,并按其指令要求进行相应操作;接收A/D采样来的数据,对数据进行处理,存储等工作。

(2)A/D控制单元。主要负责控制外部A/D芯片和多路开关的选通时序,以及实现对A/D采要过程的合理控制,利用FPGA实现A/D自动采集与数据存储。

(3)数字量监测控制单元。负责所有要监视和控制的数字量的状态数据的采集和控制命令的输出。这一部分主要实现数字量输出的控制、数字量输入的存储、数字量输入状态变化识别(中断输入)。

(4)FPGA接口逻辑控制单元。在FPGA内部设计了FPGA模块与外界MCU的接口单元,该部分主要用于同CPU的接口,使数据采集系统可以方便的与PCI、ISA及其他总线连接。

3 模拟量采集的控制与管理

在模拟量采集外围电路中,A/D芯片采用的是AD公司的AD976A。多路模拟量是通过AD438的多路开关后输入到AD976A芯片的。

A/D采样部分可分为:寄存器组、时钟发生模块、采样控制状态机、数据存储模块。

3.1 寄存器组

寄存器组用于设置/读取A/D的工作状态,包括:采样频率设置寄存器、工作模式选择寄存器、工作状态寄存器及FIFO中断寄存器。

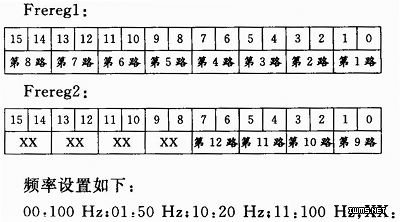

(1)采样频率设置寄存器Frereg1,Frereg2(R/W):两个16位寄存器,用于设置12路A/D的采样频率,其位含义如下:

频率设置如下:

为保留位。

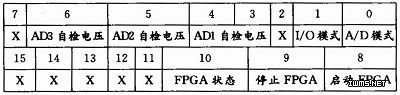

(2)工作模式选择寄存器modereg(R/W)。176位寄存器,用于设置A/D的工作模式和启动、停止FPGA,各位的定义如下:

(3)FIFO中断寄存器(fifo_int)(R):16位寄存器,用来记录FIFO的状态,各位定义如下: