・上一文章:基于FPGA的远距离测温器数控系统设计

・下一文章:基于FPGA的交通灯系统控制设计

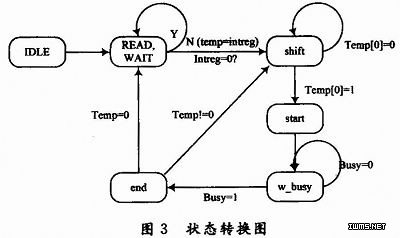

3.3 采样控制状态机

每个A/D用一个采样控制状态机,用于自动控制A/D的数据采集。其状态转换图如图3所示。

IDLE:空闲状态。

READ:temp=intreg,进入下一状态

WAIT:等待中断,如果中断寄存器(intreg)不为0,进入下一状态,否则返回READ。

SHIFT:根据temp[0]的值进行下一步操作,若temp[0]=0则temp>>1,同时通道计数器(counter)加1;若temp[0]=1,则根据counter的值给出通道选择信号,进入下一状态。

START:发出RC=0信号,进入下一状态。

W_BLISY:RC=1,等待A/D转换结束信号,如果结束,temp>>1,发出写FIFO信号,进入下一状态。

END:无效FIFO写信号,若temp=0,表明已无中断,coutnter=0,进入WAIT;否则,counter+1,进入SHIFT。

3.4 数据存储模块

用于存储A/D转换结果,对于每路A/D用一个FIFO。

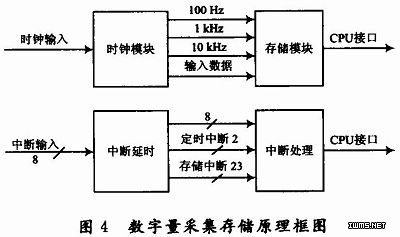

4 数字采集模块

数字采集模块主要完成数字量输入的采集与存储,中断信号状态识别功能。其原理图如图4所示。

5 结论

本文提出了一种基于FPGA技术的多路模拟量、数字量采集与处理系统,设计了相应的外围硬件电路和系统处理软件。在仿真和综合调试成功的基础上,本系统成功用于某重点预研项目的控制系统试验中。试验结果表明,本系统成功地完成了对多路模拟量、数字量的采集处理任务。