摘要:为了对交通灯系统进行精确控制,采用FPGA实验板,在QuartusⅡ软件环境下,分别实现脉冲发生模块、状态定时模块、交通灯显示模块、时间显示模块,进行仿真实验和硬件下载,获得的测试结果满足设计要求。由于采用了EDA技术,使数字系统设计的效率显著提高。

关键词:FPGA;QuartusⅡ;交通灯;数字系统设计

目前交通灯广泛应用于道路交通建设中。本文设计一个十字路口交通灯控制电路,要求东西、南北两条干道的红、绿、黄交通灯按要求循环变化,并以倒计时方式指示干道通行或禁止的维持时间。在QuartusⅡ软件环境中设计、仿真,并在FPGA实验板上实现所设计电路的功能。

1 系统概述

1.1 设计思想

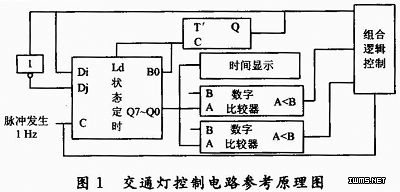

基于FPGA的交通灯系统控制设计包括4大模块,分别为脉冲发生、状态定时、交通灯闪烁的控制、闪烁时间的控制,基本原理如图1所示。

1.2 总体工作情况

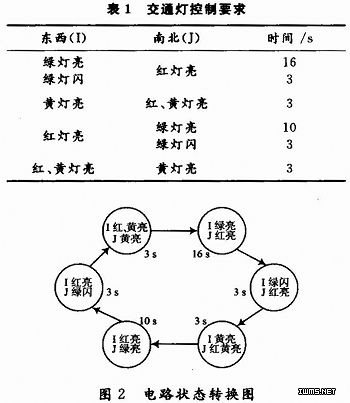

交通灯控制要求如表1所示。

该设计的交通灯控制分为6个状态。由于各状态持续时间不同,所以电路的核心控制部分是状态机和定时器,状态机在定时器触发下周期性循环,状态码控制6个灯以一定的规律变化。变化情况如图2所示。

系统脉冲由FPGA开发板晶振经过分频电路实现。状态定时由74190可逆十进制计数器和T’触发器实现,只要置数合理,翻转信号到位,就可以使电路在东西(I)、南北(J)两个控制状态间翻转。红、黄、绿灯的闪烁由7485数字比较器和组合逻辑控制,其中7485数字比较器用于比较计数器当前持续状态和所需要的状态全部时间,并做出相应的变化。组合逻辑控制由AHDL文件编写真值表实现。时间显示由AHDL文件编写真值表实现,输入正确的逻辑,七段译码电路即能得到正确的时间显示。

1.3 各功能的组成

整个电路可以分为4大部分,包括脉冲发生、状态定时、时间显示和数字比较一组合逻辑控制。

1.3.1 脉冲发生

脉冲发生器为整个系统提供驱动,将输入端分配给FPGA实验板的PIN55引脚,则会由实验板上产生频率为10 MHz的输入脉冲,用7片7490,每一级都构成10分频电路,使频率从10 MHz降低为1Hz。

1.3.2 状态定时

状态定时可由预置BCD码初值的74190级联实现,构成减计数器。级联原则是:低位计数器从全0状态变为最大码值状态时可使高位计数器减1。级联方式分为异步和同步两种,本文采取的是异步级联方式,即低位计数器溢出信号控制高位计数器的记数脉冲输入端。可根据计数器的时钟触发方式,在低位计数器状态码从全“0”变为最大码值的瞬间,为高位计数器提供有效的计数脉冲边沿。具体做法是将低片位的溢出信号RCON端口接到高片位的计数脉冲CLK,实现两位BCD码的置数、翻转和借位,使系统表示的数字能在22~16之间循环。

74190功能说明:

(1)GN为计数器使能控制端,低电平有效。当GN为高电平时,禁止计数。

(2)DNUP为计数方式控制,接高电平为减计数,接低电平为加计数。

(3)LDN为异步预置数控制。当LDN为低电平时,计数器状态QD,QC,QB,QA分别等于D,C,B,A。

(4)计数器位序由高至低顺序为QD,QC,QB,QA。QD为最高位MSB,QA为最低位LSB。

(5)计数脉冲CLK上升沿有效。

(6)当计数器输出QDQCQBQA为十进制加计数的最大状态码“1001”或为减计数的最小状态码全“0”时,极值状态码指示MAX/MIN输出为高电平。

(7)当极值状态码指示MAX/MIN为高电平且CLK为低电平时,溢出信号RCON为低电平,即RCON与计数脉冲同步。

系统记数脉冲为1 Hz时,如表2所示,当I状态(东西控制状态)的定时时间为22 s,计数器应该先预置22的BCD码;同理,J状态(南北控制状态)之前应该预置16的BCD码。