・上一文章:基于FPGA的数据采集系统设计

・下一文章:一种实时数据采集与存储系统的实现方法

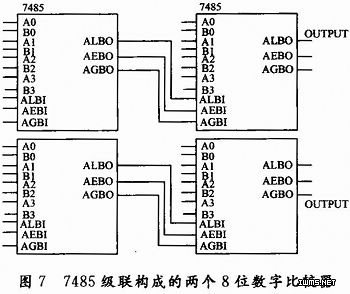

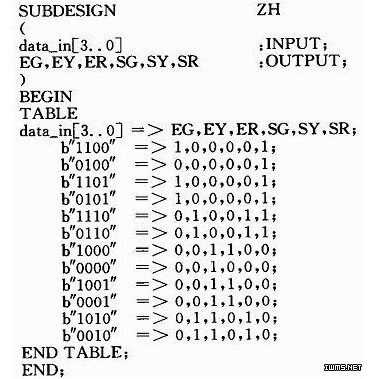

编写组合逻辑真值表,将状态信号S,两个数字比较器的输出Y1,Y2和1 Hz脉冲作为输入,各个灯的状态作为输出。从而根据逻辑关系得出对应时间电路的状态,控制红、黄、绿灯处于不同的状态。S判断电路处于22 s状态还是16 s状态,Y1,Y2区分东西、南北六个阶段状态,1 Hz脉冲实现绿灯闪烁。

2 电路的组构与调试

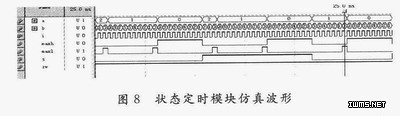

来用QuartusⅡ软件设计各个模块,并进行仿真。确认结果后,下载至FPGA实验板中,进行相应的硬件调试,调试结果与仿真结果相一致。图8为仿真波形,系统上电需要调整的过程,因此电路正常工作前重复了22s的状态。