・上一文章:串联电池电压及温度测量方法研究

・下一文章:单相桥式PWM逆变器死区补偿的一种方法

4 设计方法和仿真结果

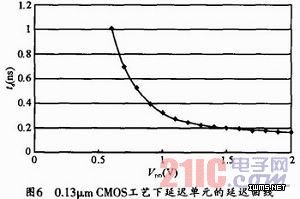

延迟单元对精度要求较高,采用全定制设计,而译码电路对精度要求较低,采用基于标准库单元设计,整体电路使用Hsim进行数模混合仿真。

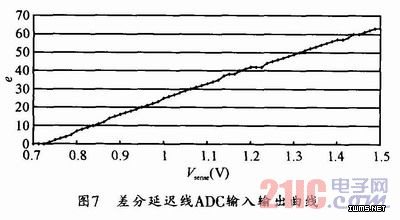

设计时,基准电压为1.5V,工作频率是1.5MHz,输入电压从0.7~1.5V线性上升,输出为译码后的结果,即6位数字信号e。Vsense每增加或减少12.5mV,e增加或减少“1”,但e的最大值是63。图7为0.13μm CMOS工艺下差分延迟线ADC的输入输出曲线,可以看出,差分延迟线ADC的输出没有明显偏移,零输入对应零输出,线性度良好。

5 结束语

本文在分析了应用于数字控制DC/DC变换器中的ADC的特点的基础上,研究了差分延迟线ADC的建模和实现。该差分延迟线ADC电路结构简单,不需要外部电路产生控制信号,可抵消部分工艺偏差。该ADC转换速率很快,功耗低,适合应用在高频数字DC/DC变换器中。